Rev. 5.00, 09/03, page 739 of 760

Appendix B Memory-Mapped Control Registers

B.1 Register Address Map

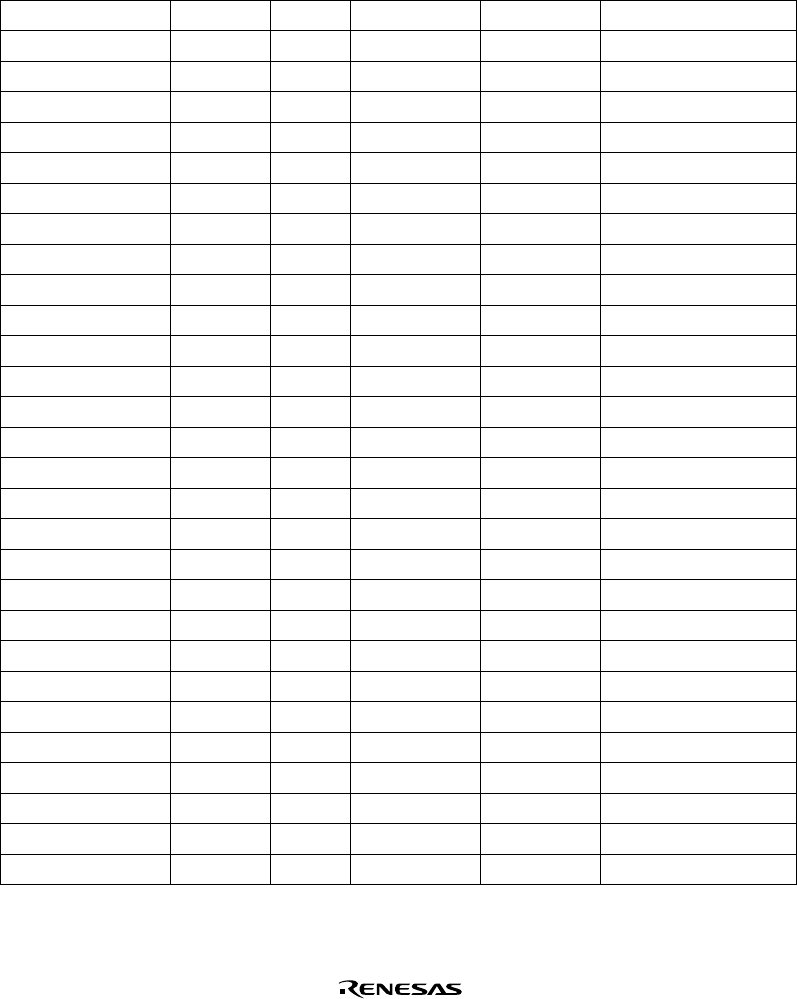

Table B.1 Memory-Mapped Control Registers

Control Register Module

*

1

Bus

*

2

Address

*

4

Size (Bits) Access Size (Bits)

3.

PTEH CCN L FFFFFFF0 32 32

PTEL CCN L FFFFFFF4 32 32

TTB CCN L FFFFFFF8 32 32

TEA CCN L FFFFFFFC 32 32

MMUCR CCN L FFFFFFE0 32 32

BASRA CCN L FFFFFFE4 32 32

BASRB CCN L FFFFFFE8 32 32

CCR CCN L FFFFFFEC 32 32

CCR2 CCN I 40000B0 32 32

TRA CCN L FFFFFFD0 32 32

EXPEVT CCN L FFFFFFD4 32 32

INTEVT CCN L FFFFFFD8 32 32

BARA UBC L FFFFFFB0 32 32

BAMRA UBC L FFFFFFB4 32 32

BBRA UBC L FFFFFFB8 16 16

BARB UBC L FFFFFFA0 32 32

BAMRB UBC L FFFFFFA4 32 32

BBRB UBC L FFFFFFA8 16 16

BDRB UBC L FFFFFF90 32 32

BDMRB UBC L FFFFFF94 32 32

BRCR UBC L FFFFFF98 16 16

BETR UBC L FFFFFF9C 16 16

BRSR UBC L FFFFFFAC 32 32

BRDR UBC L FFFFFFBC 32 32

FRQCR CPG I FFFFFF80 16 16

STBCR CPG I FFFFFF82 8 8

STBCR2 CPG I FFFFFF88 8 8

WTCNT CPG I FFFFFF84 8 16