Rev. 5.00, 09/03, page 457 of 760

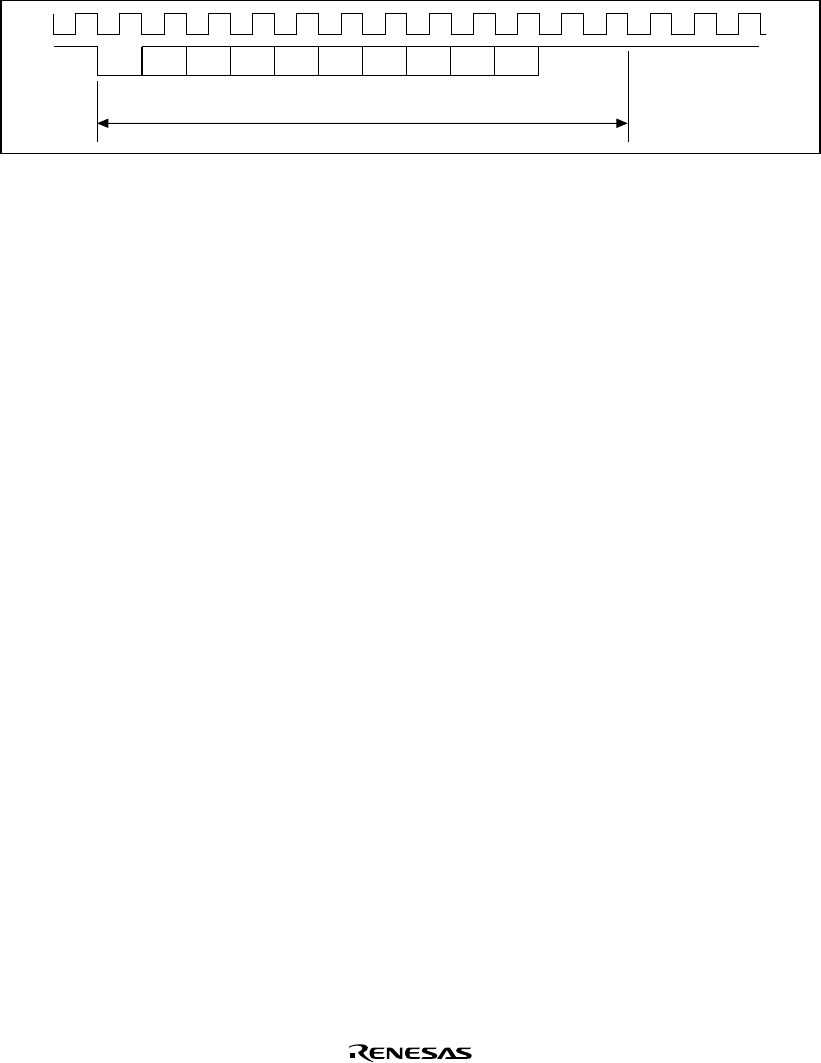

When the SCI operates on an internal clock, it can output a clock signal at the SCK pin. The

frequency of this output clock is equal to the bit rate. The phase is aligned as in figure 14.6 so that

the rising edge of the clock occurs at the center of each transmit data bit.

0 D0D1D2D3D4D5D6D70/1 1 1

1 frame

Figure 14.6 Output Clock and Serial Data Timing (Asynchronous Mode)

Transmitting and Receiving Data (SCI Initialization (Asynchronous Mode)): Before

transmitting or receiving, clear the TE and RE bits to 0 in the serial control register (SCSCR), then

initialize the SCI as follows.

When changing the operation mode or communication format, always clear the TE and RE bits to

0 before following the procedure given below. Clearing TE to 0 sets TDRE to 1 and initializes the

transmit shift register (SCTSR). Clearing RE to 0, however, does not initialize the RDRF, PER,

FER, and ORER flags or receive data register (SCRDR), which retain their previous contents.

When an external clock is used, the clock should not be stopped during initialization or subsequent

operation. SCI operation becomes unreliable if the clock is stopped.

Figure 14.7 shows a sample flowchart for initializing the SCI. The procedure for initializing the

SCI is:

1. Select the clock source in the serial control register (SCSCR). Leave RIE, TIE, TEIE, MPIE,

TE, and RE cleared to 0. If clock output is selected in asynchronous mode, clock output starts

immediately after the setting is made in SCSCR.

2. Select the communication format in the serial mode register (SCSMR).

3. Write the value corresponding to the bit rate in the bit rate register (SCBRR) (not necessary if

an external clock is used).

4. Wait for at least the interval required to transmit or receive one bit, then set TE or RE in the

serial control register (SCSCR) to 1. Also set RIE, TIE, TEIE, and MPIE as necessary. Setting

TE or RE enables the SCI to use the TxD or RxD pin. The initial state is the mark state when

transmitting, or the idle state (waiting for a start bit) when receiving.