Rev. 5.00, 09/03, page 481 of 760

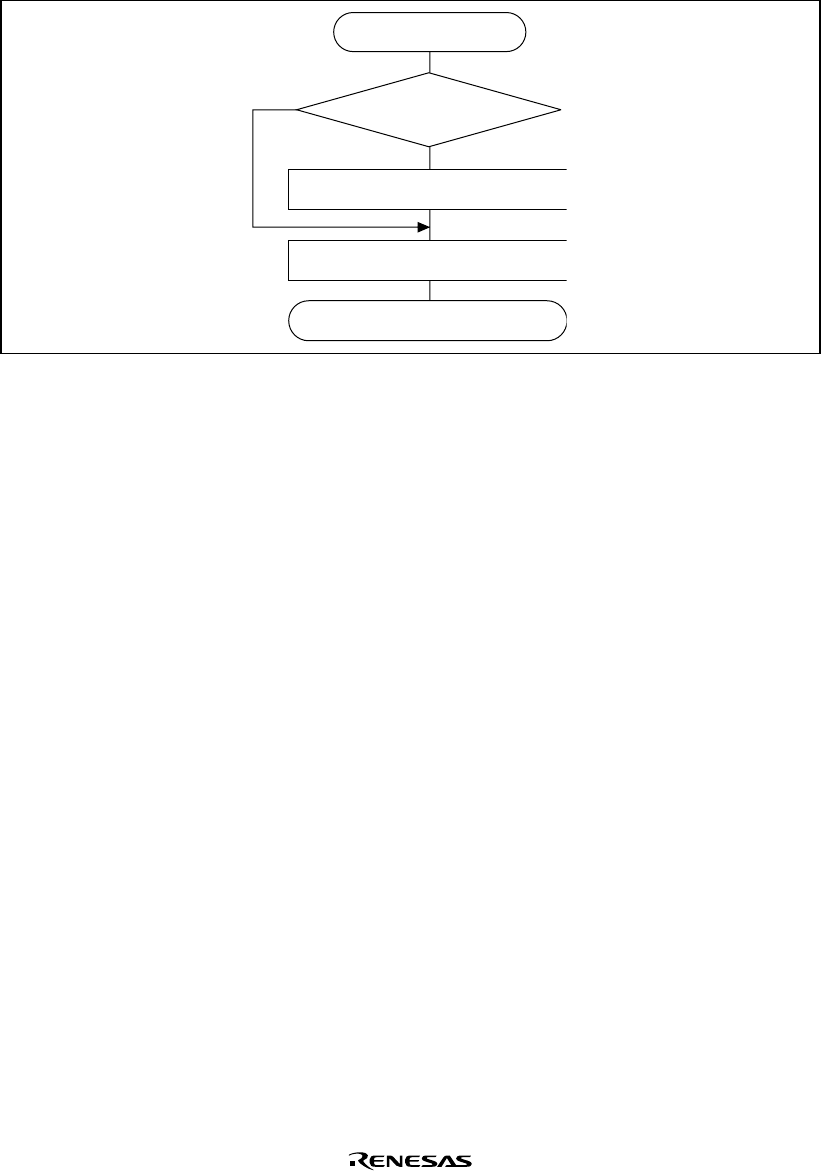

Error handling

End

ORER = 1?

No

Clear ORER bit in SCSSR to 0

Yes

Overrun error handling

Figure 14.21 Sample Flowchart for Receiving Serial Data (cont)

In receiving, the SCI operates as follows:

1. The SCI synchronizes with serial clock input or output and initializes internally.

2. Receive data is shifted into SCRSR in order from the LSB to the MSB. After receiving the

data, the SCI checks that RDRF is 0 so that receive data can be loaded from SCRSR into

SCRDR. If this check is passed, the SCI sets RDRF to 1 and stores the received data in

SCRDR. If the check is not passed (receive error), the SCI operates as indicated in table 14.12.

This state prevents further transmission or reception. While receiving, the RDRF bit is not set

to 1. Be sure to clear the error flag.

3. After setting RDRF to 1, if the receive-data-full interrupt enable bit (RIE) is set to 1 in

SCSCR, the SCI requests a receive-data-full interrupt (RXI). If the ORER bit is set to 1 and the

receive-data-full interrupt enable bit (RIE) in SCSCR is also set to 1, the SCI requests a

receive-error interrupt (ERI).

Figure 14.22 shows an example of SCI receive operation.