Rev. 5.00, 09/03, page 360 of 760

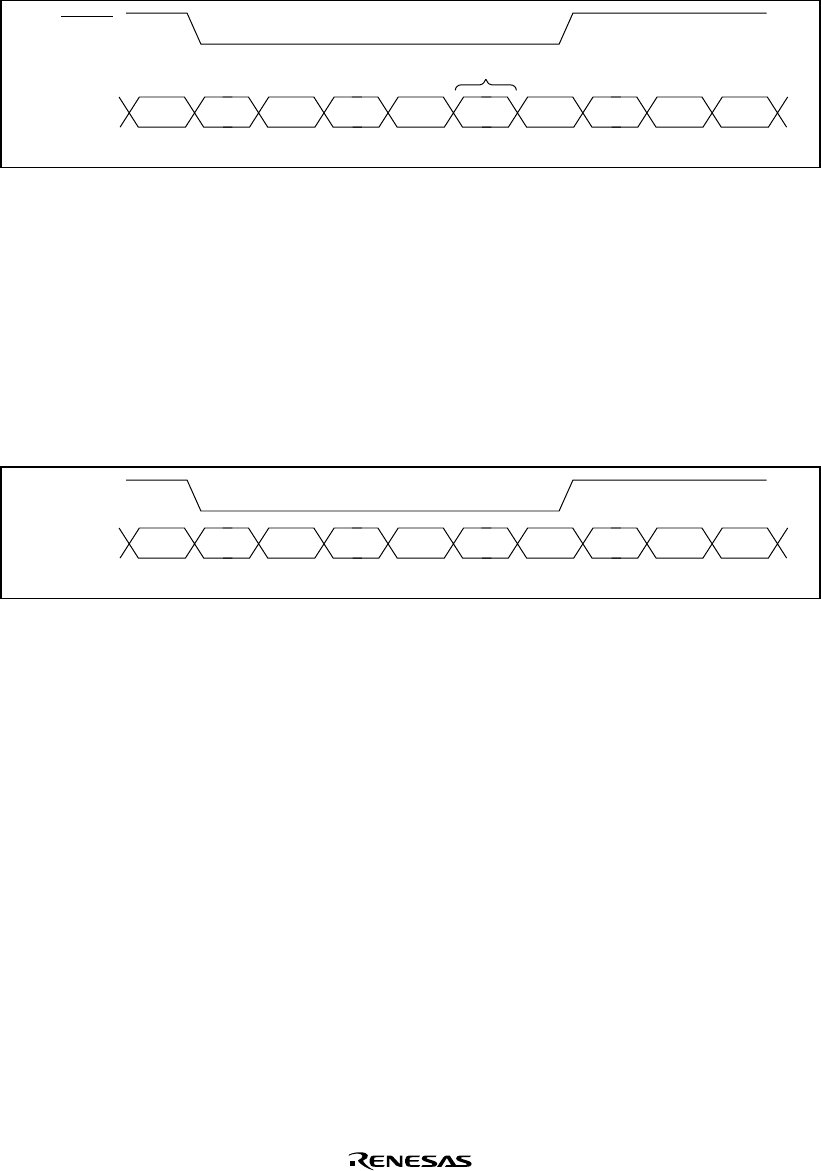

CPU CPU CPU DMAC DMAC CPU DMAC DMAC CPU CPU

DREQ

Bus cycle

Bus returned to CPU

Read Write WriteRead

Figure 11.12 Example of DMA Transfer in Cycle-Steal Mode

• Burst Mode

Once the bus is obtained, the transfer is performed continuously until the transfer end

condition is satisfied. In external request mode with low level detection of the DREQ pin,

however, when the DREQ pin is driven high, the bus passes to the other bus master after the

DMAC transfer request that has already been accepted ends, even if the transfer end conditions

have not been satisfied.

Burst mode cannot be used when a serial communication interface (IrDA, SCI), or A/D

converter is the transfer request source. Figure 11.13 shows an example of burst mode timing.

CPU CPU CPU DMAC DMAC DMAC DMACDMAC DMAC CPU

DREQ

Bus cycle

Read Read ReadWrite Write Write

Figure 11.13 Example of Transfer in Burst Mode