Rev. 5.00, 09/03, page 65 of 760

3.3.2 TLB Indexing

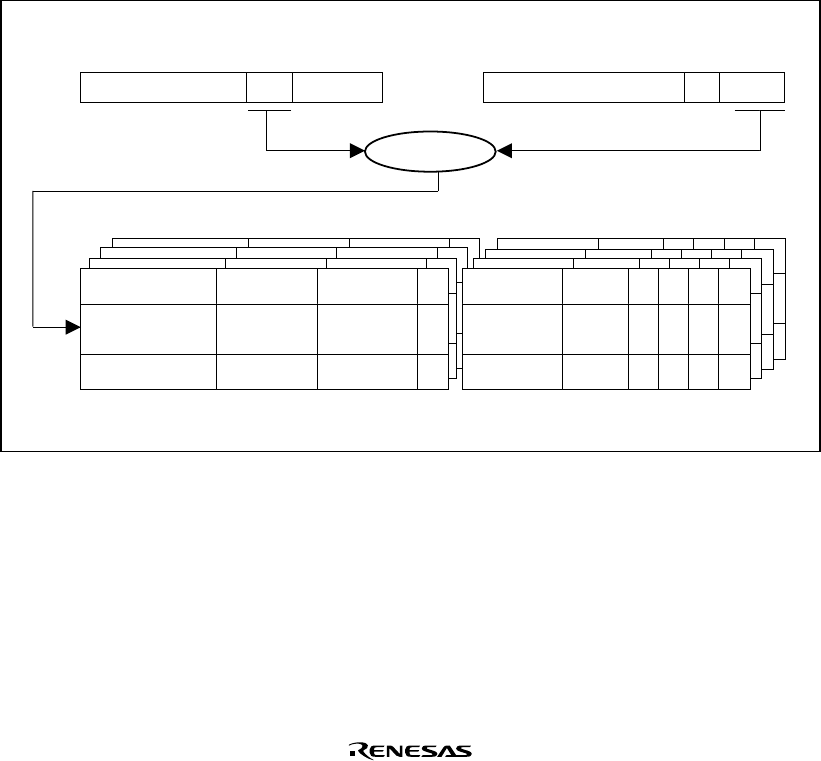

The TLB uses a 4-way set associative scheme, so entries must be selected by index. VPN bits 16

to 12 and ASID bits 4 to 0 in PTEH are used as the index number regardless of the page size. The

index number can be generated in two different ways depending on the setting of the IX bit in

MMUCR.

1. When IX = 0, VPN bits 16–12 alone are used as the index number

2. When IX = 1, VPN bits 16–12 are EX-ORed with ASID bits 4–0 to generate a 5-bit index

number

The second method is used to prevent lowered TLB efficiency that results when multiple

processes run simultaneously in the same virtual address space (multiple virtual memory) and a

specific entry is selected by generating an index number for each process. Figures 3.6 and 3.7

show the indexing schemes.

31 16 111217 0 31 0

PTEH registerVirtual address

VPN 0 ASID

710

Index

ASID(4−0)

Exclusive-OR

Ways 0−3

VPN(31−17) VPN(11−10)

ASID(7−0) V

0

31

Address array Data array

PPN(28−10) PR(1−0) SZ C D SH

Figure 3.6 TLB Indexing (IX = 1)