Rev. 5.00, 09/03, page 736 of 760

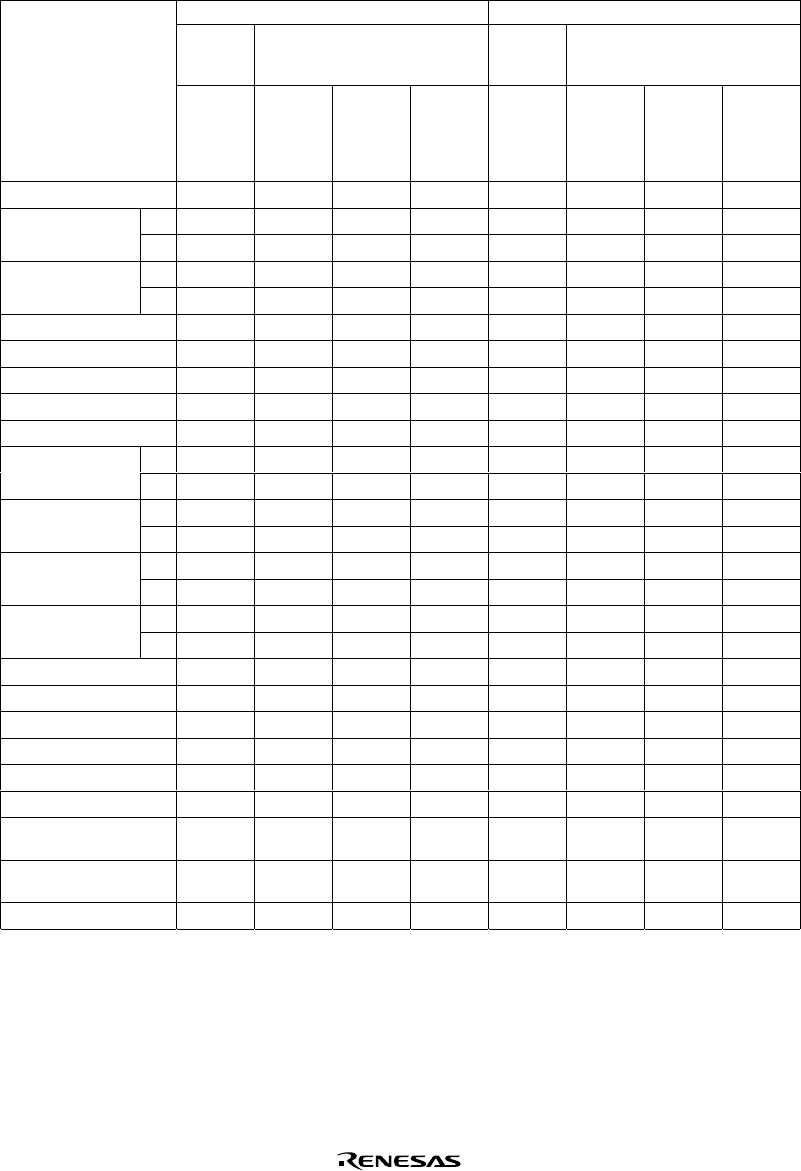

PCMCIA Memory Interface (Area 6) PCMCIA/IO Interface (Area 6)

8-Bit

Bus

Width

16-Bit Bus Width

8-Bit

Bus

Width

16-Bit Bus Width

Pin

Byte/

Word/

Long-

word

Access

Byte

Access

(Ad-

dress

2n)

Byte

Access

(Ad-

dress

2n + 1)

Word/

Long-

word

Access

Byte/

Word/

Long-

word

Access

Byte

Access

(Ad-

dress

2n)

Byte

Access

(Ad-

dress

2n+1)

Word/

Long-

word

Access

CS6 to CS2, CS0 Enabled Enabled High Enabled Enabled Enabled High Enabled

R Low Low Low Low High High High HighRD

W High High High High High High High High

R High High High High High High High HighRD/WR

W Low Low Low Low Low Low Low Low

BS Enabled Enabled Enabled Enabled Enabled Enabled Enabled Enabled

RAS3U/PTE[2] High High High High High High High High

RAS3L/PTJ[0] High High High High High High High High

CASL/PTJ[2] High High High High High High High High

CASU/PTJ[3] High High High High High High High High

R High High High High High High High HighWE0/DQMLL

W High High High High High High High High

R High High High High High High High HighWE1/DQMLU/WE

W Low Low Low Low High High High High

R High High High High Low Low Low Low

WE2/DQMUL/

ICIORD/PTK[6]

W High High High High High High High High

R High High High High High High High High

WE3/DQMUU/

ICIOWR/PTK[7]

W High High High High Low Low Low Low

CE2A/PTE[4] High High High High High High High High

CE2B/PTE[5] High High Low Low High High Low Low

CKE/PTK[5] Disabled Disabled Disabled Disabled Disabled Disabled Disabled Disabled

WAIT Enabled

*

1

Enabled

*

1

Enabled

*

1

Enabled

*

1

Enabled

*

1

Enabled

*

1

Enabled

*

1

Enabled

*

1

IOIS16/PTG[7] Disabled Disabled Disabled Disabled Disabled Disabled Enabled Enabled

A25 to A0 Address Address Address Address Address Address Address Address

D7 to D0

Valid

data

Valid

data

Invalid

data

Valid

data

Valid

data

Valid

data

Invalid

data

Valid

data

D15 to D8 High-Z

*

2

Invalid

data

Valid

data

Valid

data

High-Z

*

2

Invalid

data

Valid

data

Valid

data

D31 to D16 High-Z

*

2

High-Z

*

2

High-Z

*

2

High-Z

*

2

High-Z

*

2

High-Z

*

2

High-Z

*

2

High-Z

*

2

Notes: 1. Disabled when WCR2 register wait setting is 0.

2. Unused data pins should be switched to the port function, or pulled up.