Rev. 5.00, 09/03, page 232 of 760

Shadow Space: Areas 0 and 2–6 are decoded by physical addresses A28–A26, which correspond

to areas 000 to 110. Address bits 31–29 are ignored. This means that the range of area 0 addresses,

for example, is H'00000000 to H'03FFFFFF, and its corresponding shadow space is the address

space obtained by adding to it H'20000000 × n (n = 1–6). The address range for area 7, which is

on-chip I/O space, is H'1C000000 to H'1FFFFFFF. The address space H'1C000000 + H'20000000

× n–H'1FFFFFFF + H'20000000 × n (n = 0–7) corresponding to the area 7 shadow space is

reserved, and must not be used.

10.1.6 PCMCIA Support

The SH7709S supports PCMCIA standard interface specifications in physical space areas 5 and 6.

The interfaces supported are basically the “IC memory card interface” and “I/O card interface”

stipulated in JEIDA Specifications Ver. 4.2 (PCMCIA2.1).

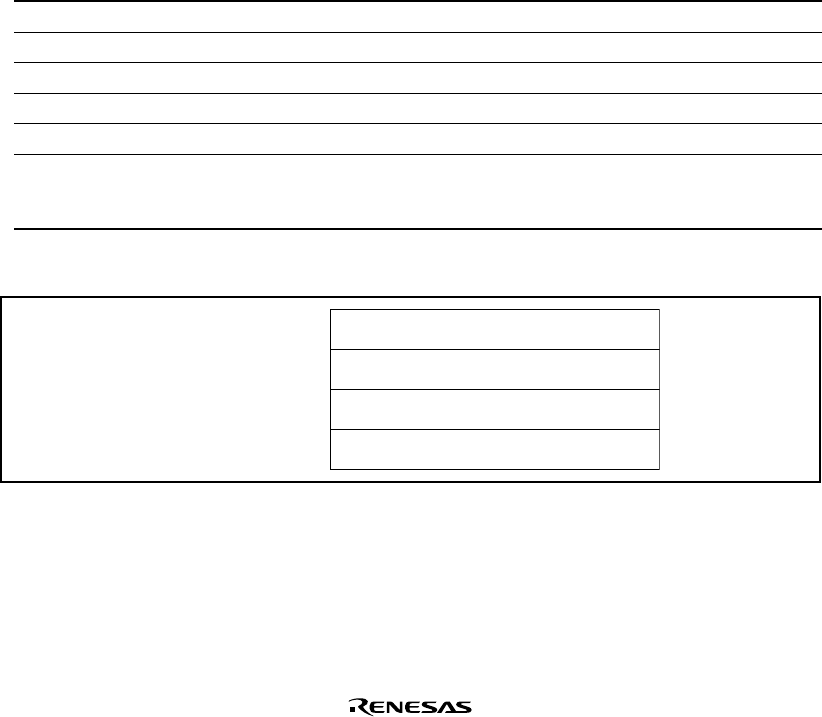

Table 10.5 PCMCIA Interface Characteristics

Item Feature

Access Random access

Data bus 8/16 bits

Memory type Mask ROM, OTPROM, EPROM, EEPROM, flash memory, SRAM

Memory capacity Maximum 32 Mbytes

I/O space capacity Maximum 32 Mbytes

Other features Dynamic bus sizing of I/O bus width

*

The PCMCIA interface can be accessed from the address translation

area or non-address translation area.

Note: * Dynamic bus sizing of the I/O bus width is supported only in little-endian mode.

Common memory/Attribute memoryArea 5: H'14000000

Area 5: H'16000000

Common memory/Attribute memoryArea 6: H'18000000

I/O space

I/O space

A

rea 6: H'1A000000

Figure 10.4 PCMCIA Space Allocation