Rev. 5.00, 09/03, page 91 of 760

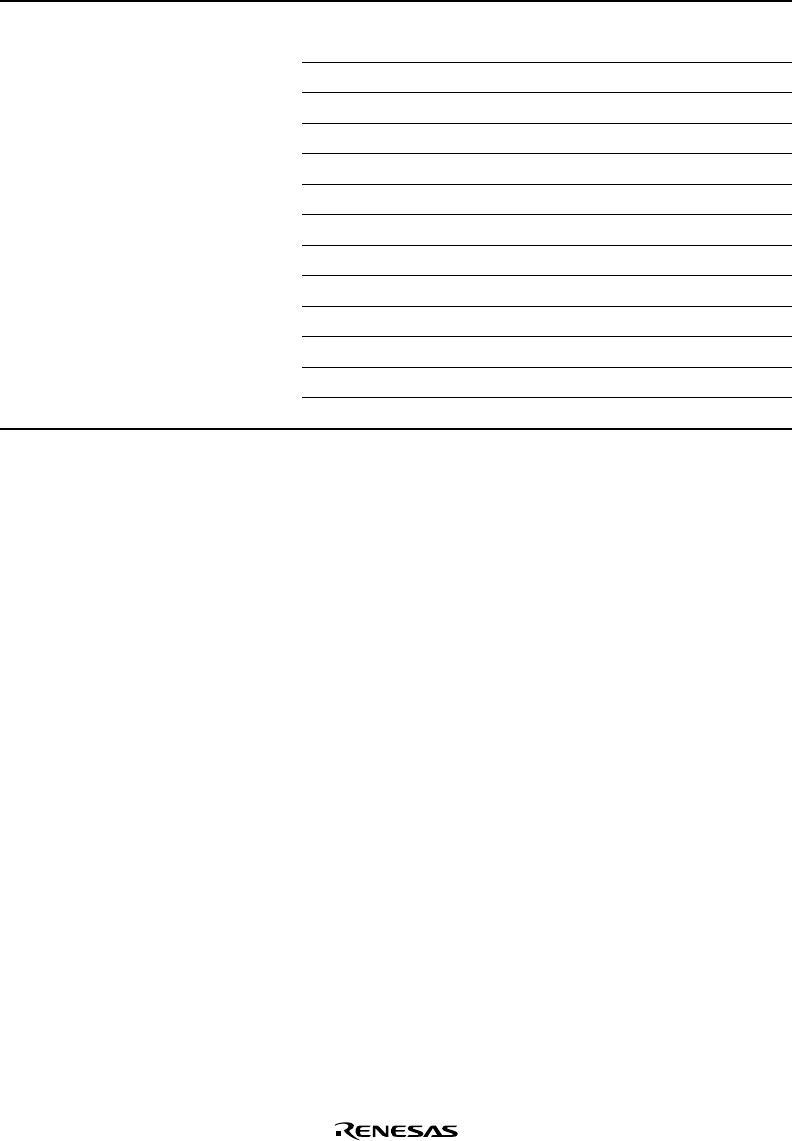

Exception Type Exception Event Exception Code

General interrupt requests External hardware interrupts (cont):

(cont)

IRL3–IRL0

= 0010 H'240

IRL3–IRL0

= 0011 H'260

IRL3–IRL0

= 0100 H'280

IRL3–IRL0

= 0101 H'2A0

IRL3–IRL0

= 0110 H'2C0

IRL3–IRL0

= 0111 H'2E0

IRL3–IRL0

= 1000 H'300

IRL3–IRL0

= 1001 H'320

IRL3–IRL0

= 1010 H'340

IRL3–IRL0

= 1011 H'360

IRL3–IRL0

= 1100 H'380

IRL3–IRL0

= 1101 H'3A0

IRL3–IRL0

= 1110 H'3C0

4.2.5 Exception Request Masks

When the BL bit in SR is 0, exceptions and interrupts are accepted.

If a general exception event occurs when the BL bit in SR is 1, the CPU’s internal registers are set

to their post-reset state, other module registers retain their contents prior to the general exception,

and a branch is made to the same address (H'A0000000) as for a reset.

If a general interrupt occurs when BL = 1, the request is masked (held pending) and not accepted

until the BL bit is cleared to 0 by software. For reentrant exception handling, SPC and SSR must

be saved and the BL bit in SR cleared to 0.

4.2.6 Returning from Exception Handling

The RTE instruction is used to return from exception handling. When RTE is executed, the SPC

value is set in PC, and the SSR value in SR, and the return from exception handling is performed

by branching to the SPC address.

If SPC and SSR have been saved in external memory, set the BL bit in SR to 1, then restore SPC

and SSR, and issue an RTE instruction.