Rev. 5.00, 09/03, page 652 of 760

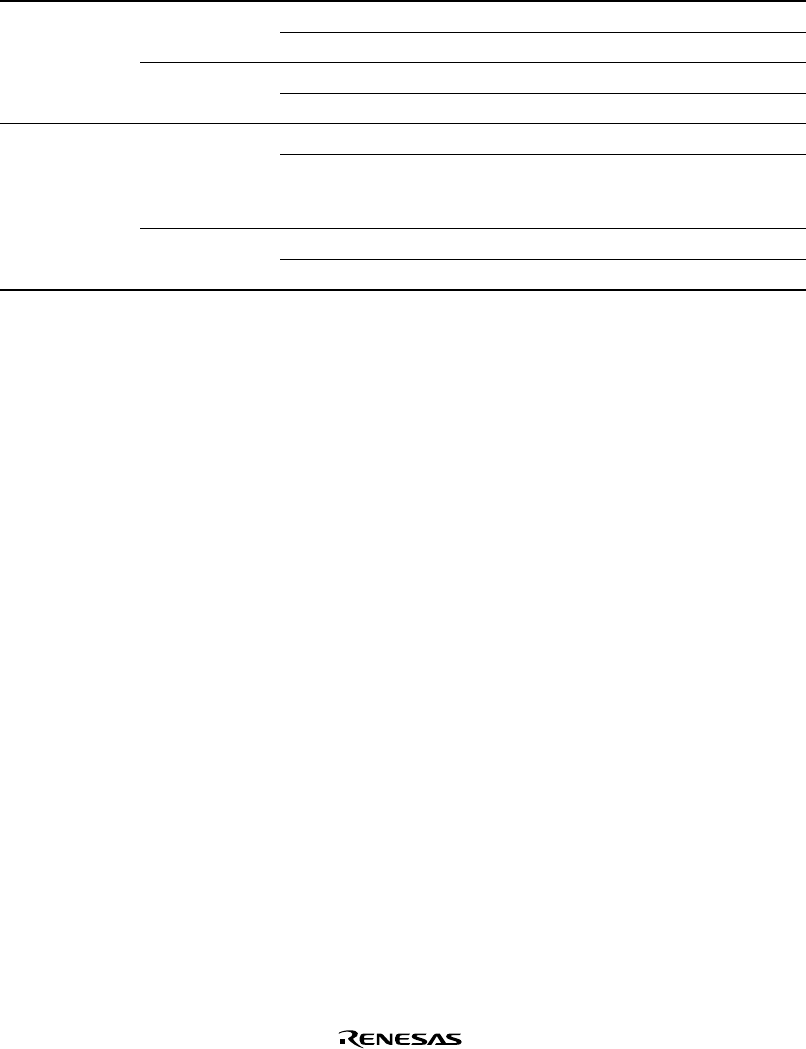

22.4.2 Reset Configuration

Table 22.4 Reset Configuration

ASE

ASEASE

ASEM

MM

MD

DD

D0

00

0

*

1

R

RR

RESE

ESEESE

ESET

TT

TP

PP

PT

TT

TR

RR

RS

SS

ST

TT

T Chip State

High-level Low-level Low-level Normal reset and UDI reset

High-level Normal reset

High-level Low-level UDI reset only

High-level Normal operation

Low-level Low-level Low-level Reset hold

*

2

High-level ASE user mode

*

3

: Normal reset

ASE break mode

*

3

: RESETP assertion

masked

High-level Low-level UDI reset only

High-level Normal operation

Notes: 1. Selects main chip mode or ASE mode

ASEMD0 = H, normal mode

ASEMD0 = L, ASE mode

Set ASEMD0 = H when using on the user system alone, without an emulator and the

UDI.

2. In ASE mode, reset hold is enabled by driving the RESETP and TRST pins low for a

constant cycle. In this state, the CPU does not start up, even if RESETP is driven high.

When TRST is driven high, UDI operation is enabled, but the CPU does not start up.

The reset hold state is cancelled by the following:

• Boot request from UDI

• Another RESETP assert (power-on reset)

3. There are two ASE modes, one for executing software in the emulator’s firmware (ASE

break mode) and one for executing user software (ASE user mode).