Rev. 5.00, 09/03, page 679 of 760

t

RSD

t

AH

t

RSD

t

AH

t

AH

t

RDH1

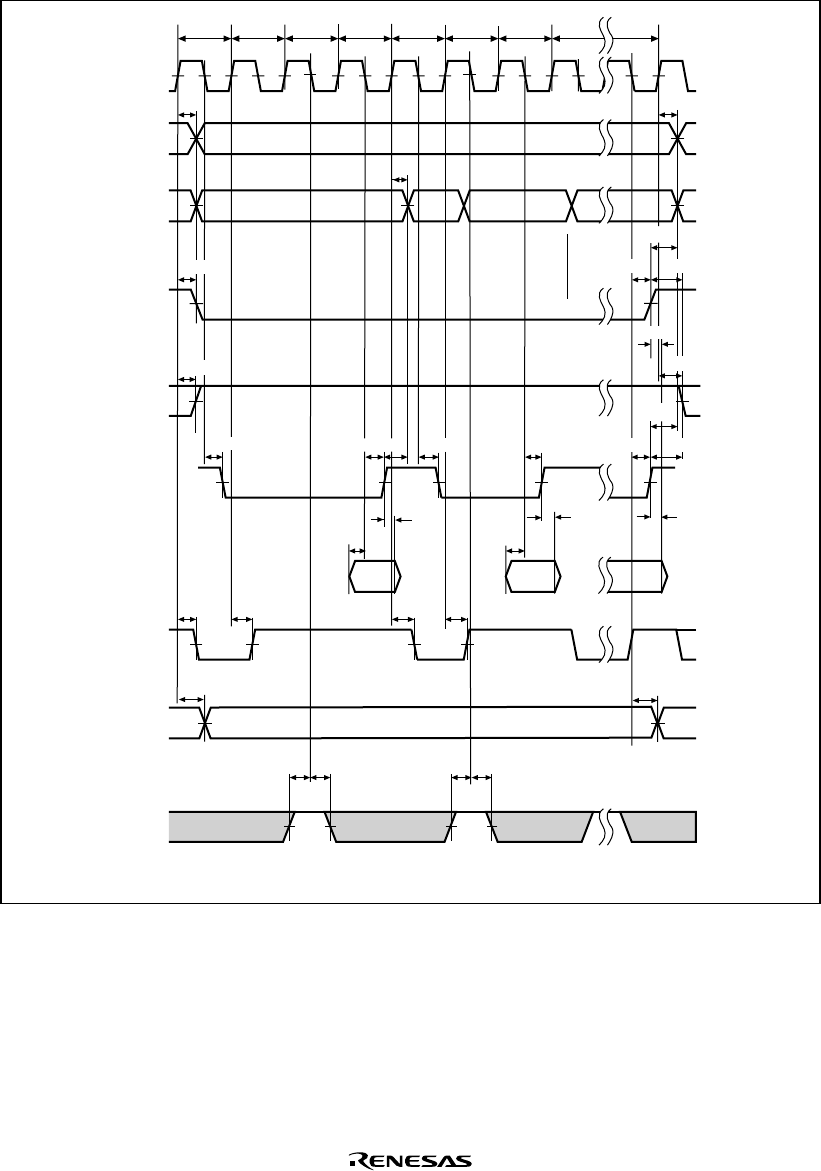

CKIO

A25 to A4

A3 to A0

CSn

RD/WE

RD

D31 to D0

Note: In the write cycle, the basic bus cycle is performed.

BS

WAIT

DACKn

t

AD

t

AD

t

AD

t

CSD1

t

RWH

t

RWD

t

RSD

t

RSD

t

RDH1

t

RDH1

t

RDS1

t

BSD

t

DAKD1

t

DAKD2

t

BSD

t

BSD

t

BSD

t

WTS

t

WTH

t

WTS

t

WTH

T

1

T

w

T

w

T

B2

T

B1

T

B2

T

w

T

2

T

2

t

CSD2

t

RDS1

t

RDH1

t

RSD

t

RWD

t

RWH

Figure 23.20 Burst ROM Bus Cycle (Two Waits)