Rev. 5.00, 09/03, page 277 of 760

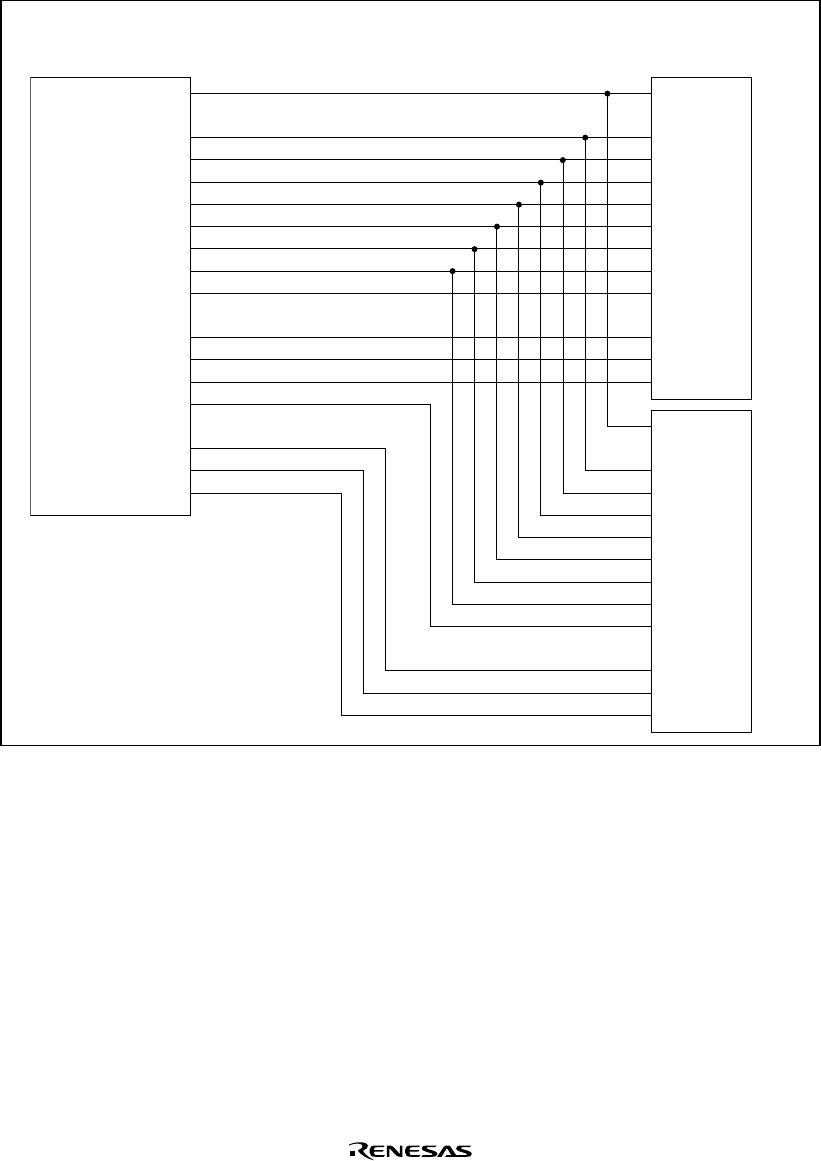

A15

A2

CKI0

CKE

CSn

RAS3x

CASx

RD/WR

D31

D16

DQMUU

DQMUL

D15

D0

DQMLU

DQMLL

SH7709S

64M synchronous

DRAM

(1M × 16-bit × 4-bank

)

••••

A13

A0

CLK

CKE

CS

RAS

CAS

WE

DQ15

DQ0

DQMU

DQML

••••

••••

••••

A13

A0

CLK

CKE

CS

RAS

CAS

WE

DQ15

DQ0

DQMU

DQML

••••••••

••••••••••••••••

••••

••••••••••••

Note : "x" is U or L

Figure 10.12 Example of 64-Mbit Synchronous DRAM Connection (32-Bit Bus Width)