Rev. 5.00, 09/03, page 329 of 760

11.1.2 Block Diagram

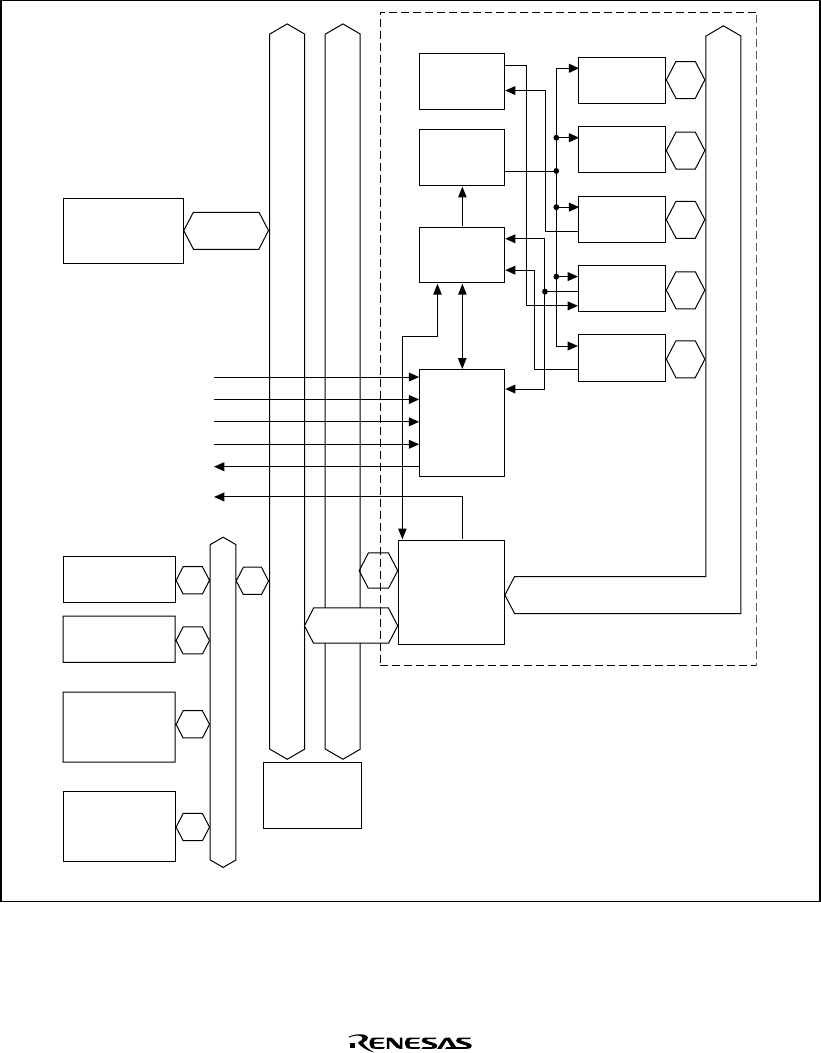

Figure 11.1 shows a block diagram of the DMAC.

Peripheral bus

Internal bus

DREQ0, DREQ1

Iteration

control

SARn

DMAC module

Register

control

Start-up

control

Request

priority

control

Bus interface

Bus state

controller

On-chip

peripheral

module

DARn

DMATCRn

CHCRn

DMAOR

IrDA, SCIF

A/D converter

CMT

DEIn

External

RAM

External

ROM

External I/O

(memory

mapped)

External I/O

(with

acknowledge)

DACK0, DACK1

DRAK0, DRAK1

Legend

DMAOR:

SARn:

DARn:

DMATCRn:

CHCRn:

DEIn:

n = 0 to 3

DMAC operation register

DMAC source address register

DMAC destination address register

DMAC transfer count register

DMAC channel control register

DMA transfer-end interrupt request to

CPU

Figure 11.1 Block Diagram of DMAC