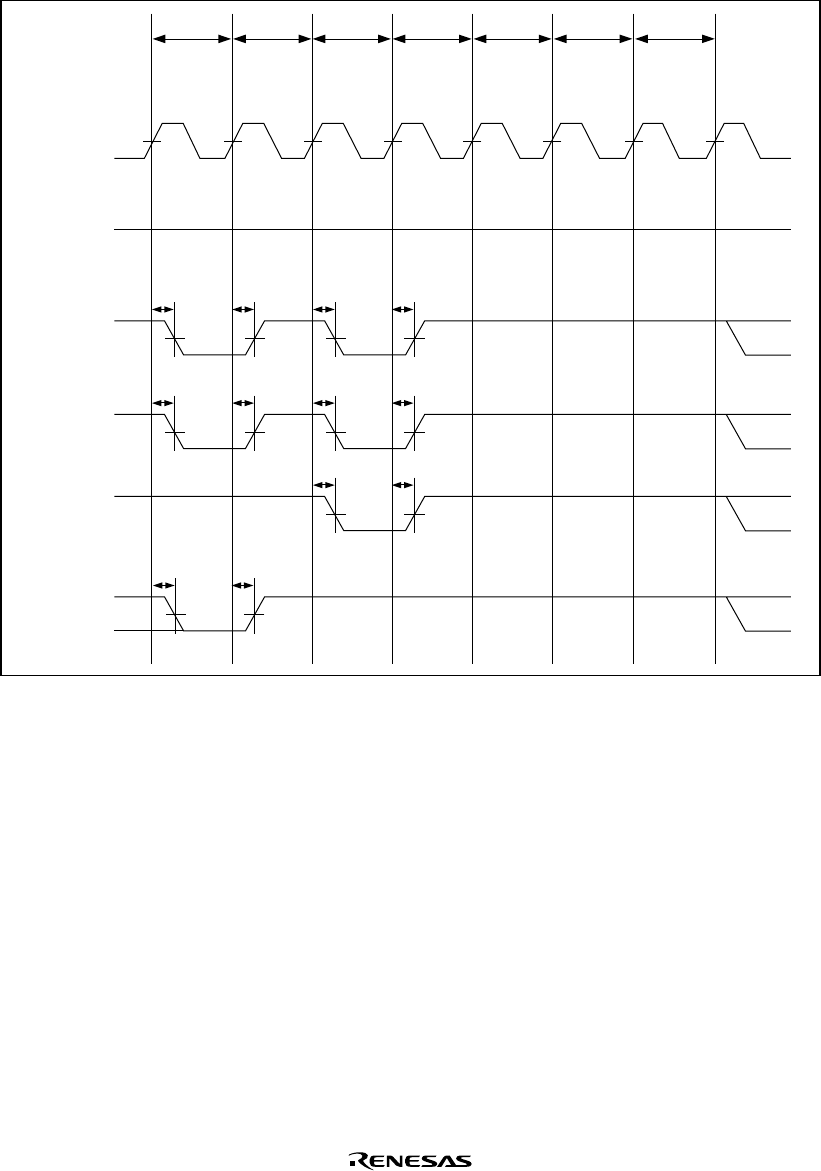

Rev. 5.00, 09/03, page 696 of 760

CKIO

CSn

RD/WR

CASxx

CKE

RAS3x

Tp

Tpc TRr TRrw TRrw (Tpc) (Tpc)

t

CSD3

t

CSD3

t

CSD3

t

CSD3

t

RASD2

t

RASD2

t

RASD2

t

RASD2

t

CASD2

t

CASD2

t

RWD

t

RWD

(High)

Figure 23.37 Synchronous DRAM Auto-Refresh Timing (TRAS = 1, TPC = 1)