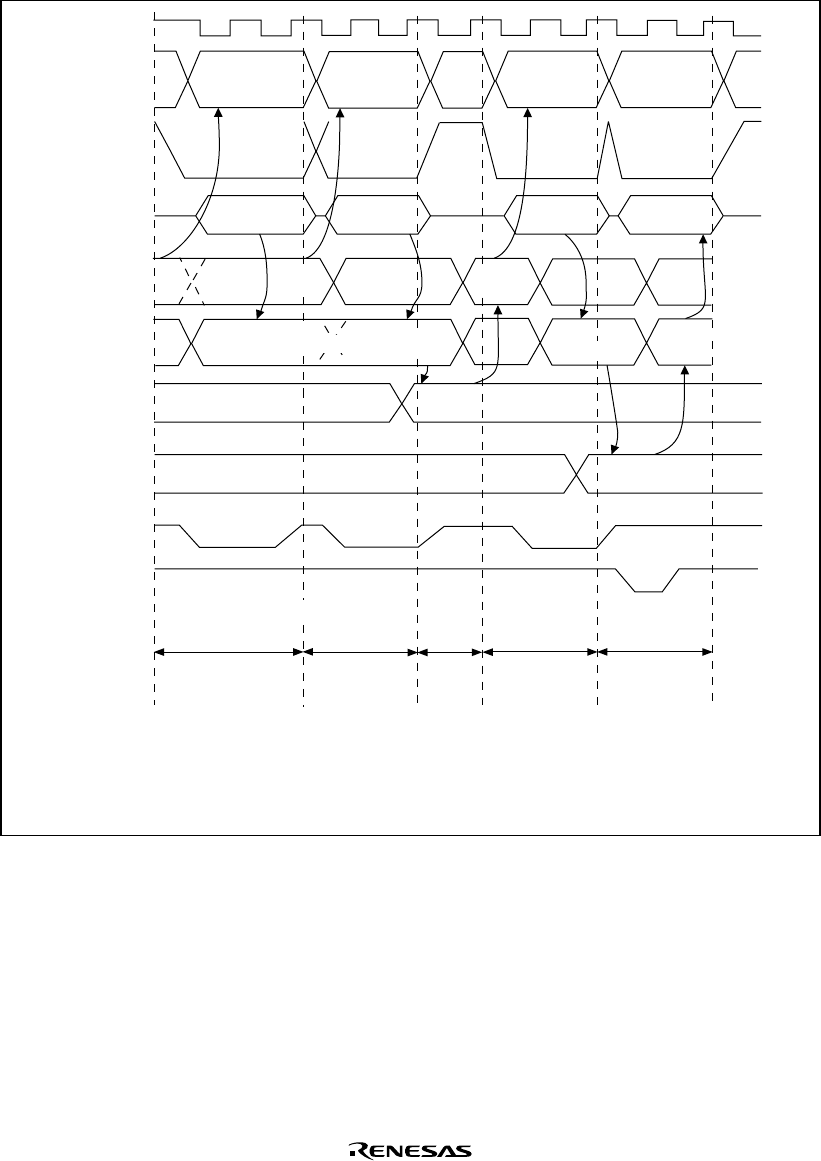

Rev. 5.00, 09/03, page 356 of 760

Transfer

source

address (H)

Transfer

source

address (L)

Indirect

address

NOP

Transfer

destination

address

Indirect

address (H)

Indirect

address (L)

Transfer

data

Transfer

data

Transfer

data

Transfer

data

Transfer

data

Transfer source

address

*1

Transfer source address

*2

Indirect

address

NOP

Indirect

address

Address read cycle

(1st)

(2nd) (3rd)

NOP

cycle

Data

read cycle

(4th)

Data

write cycle

CKIO

A25 to A0

CSn

D31 to D0

Internal

address

bus

Internal

data bus

DMAC

indirect

address

buffer

DMAC

data

buffer

RD

WEn

Notes: 1.

2.

The internal address bus value does not change, and is controlled by the port.

The DMAC does not fetch the value until 32-bit data is output to the internal data bus.

External memory space → external memory space (external memory is 16-bit width)

Figure 11.8 Example of Transfer Timing in the Indirect Address Mode

in Dual Address Mode