Rev. 5.00, 09/03, page 151 of 760

7.1.3 Register Configuration

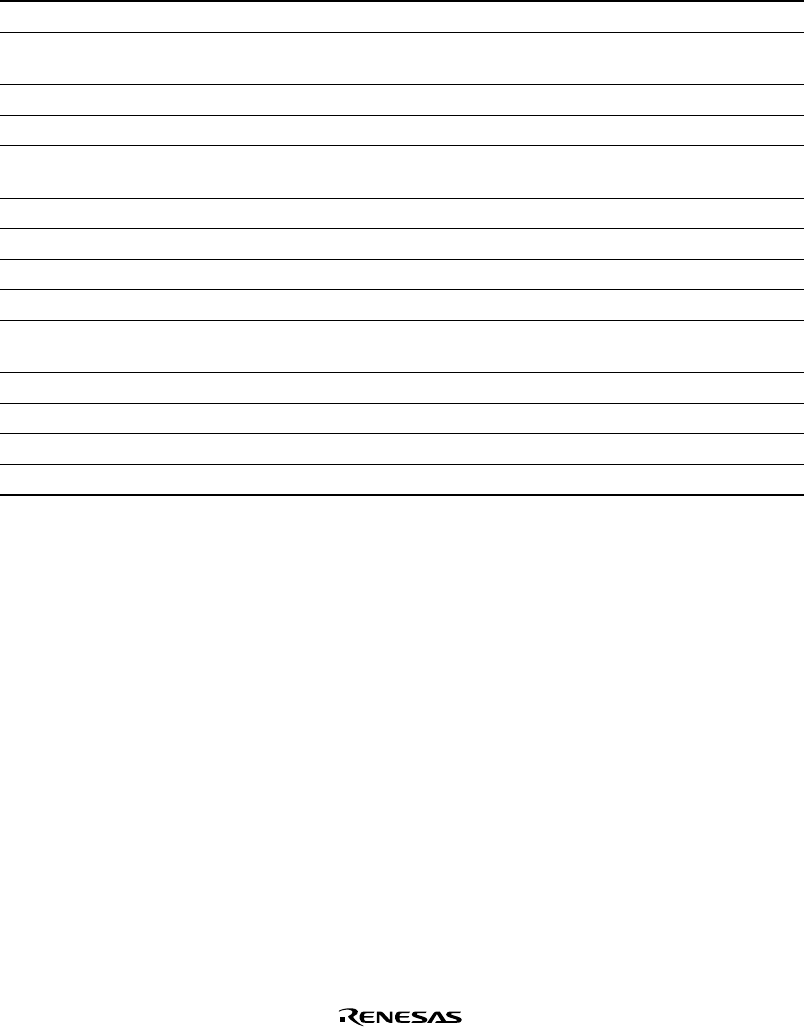

Table 7.1 Register Configuration

Name Abbr. R/W Initial Value

*

1

Address

Access

Size Location

Break address register A BARA R/W H'00000000 H'FFFFFFB0 32 UBC

Break address mask

register A

BAMRA R/W H'00000000 H'FFFFFFB4 32 UBC

Break bus cycle register A BBRA R/W H'0000 H'FFFFFFB8 16 UBC

Break address register B BARB R/W H'00000000 H'FFFFFFA0 32 UBC

Break address mask

register B

BAMRB R/W H'00000000 H'FFFFFFA4 32 UBC

Break bus cycle register B BBRB R/W H'0000 H'FFFFFFA8 16 UBC

Break data register B BDRB R/W H'00000000 H'FFFFFF90 32 UBC

Break data mask register B BDMRB R/W H'00000000 H'FFFFFF94 32 UBC

Break control register BRCR R/W H'00000000 H'FFFFFF98 32 UBC

Execution count break

register

BETR R/W H'0000 H'FFFFFF9C 16 UBC

Branch source register BRSR R Undefined

*

2

H'FFFFFFAC 32 UBC

Branch destination register BRDR R Undefined

*

2

H'FFFFFFBC 32 UBC

Break ASID register A BASRA R/W Undefined H'FFFFFFE4 16 CCN

Break ASID register B BASRB R/W Undefined H'FFFFFFE8 16 CCN

Notes: 1. Initialized by power-on reset. Values held in standby state and undefined by manual

resets.

2. Bit 31 of BRSR and BRDR (valid flag) is initialized by power-on resets. But other bits

are not initialized.