Rev. 5.00, 09/03, page 280 of 760

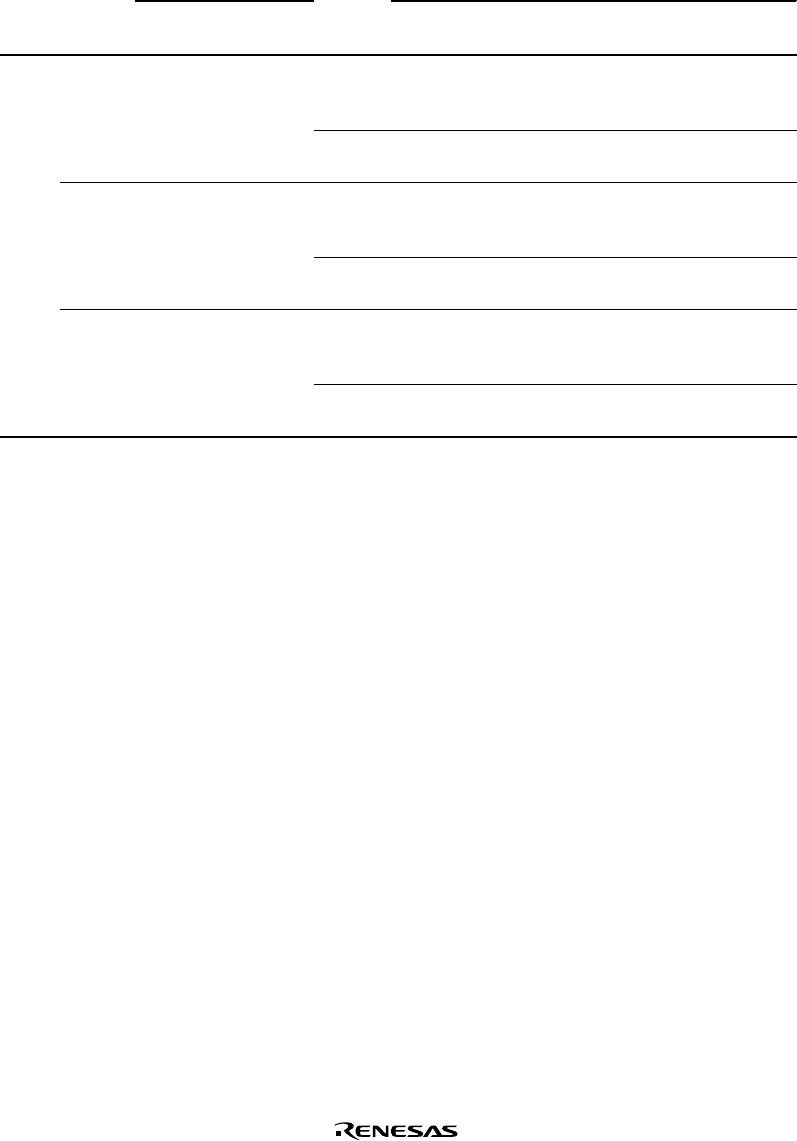

Setting External Address Pins

Bus

Width

Memory

Type

AMX

3

AMX

2

AMX

1

AMX

0

Output

Timing

A1 to

A8 A9 A10 A11 A12 A13 A14 A15 A16

2M ×

16bits ×

4banks

*

2

0101Column

address

A1 to

A8

A9 A10 L/H

*

3

A12 A22

*

4

A23

*

4

A24

Row

address

A10 to

A17

A18 A19 A20 A21 A22

*

4

A23

*

4

A24

1M ×

16bits ×

4banks

*

2

0100Column

address

A1 to

A8

A9 A10 L/H

*

3

A12 A21

*

4

A22

*

4

A15

Row

address

A 9 to

A16

A17 A18 A19 A20 A21

*

4

A22

*

4

A23

2M ×

8bits ×

4banks

*

2

0101Column

address

A1 to

A8

A9 A10 L/H

*

3

A12 A22

*

4

A23

*

4

A24

Row

address

A10 to

A17

A18 A19 A20 A21 A22

*

4

A23

*

4

A24

Notes: 1. Only RAL3L or CASL is output.

2. When addresses are upper 32 Mbytes, RAS3U or CASU is output.

When addresses are lower 32 Mbytes, RAS3L or CASL is output.

3. L/H is a bit used in the command specification; it is fixed at L or H according to the

access mode.

4. Bank address specification