Rev. 5.00, 09/03, page 534 of 760

16.2.9 FIFO Control Register (SCFCR)

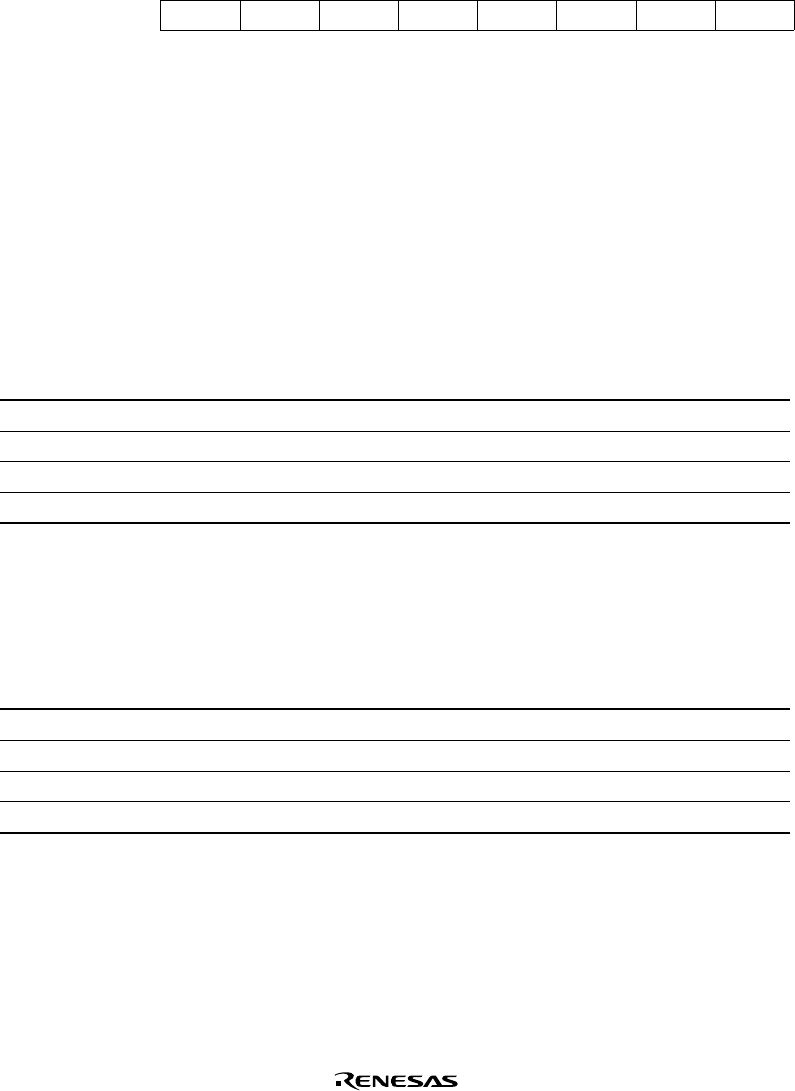

Bit:76543210

RTRG1 RTRG0 TTRG1 TTRG0 MCE TFRST RFRST LOOP

Initial value:00000000

R/W: R/W R/W R/W R/W R/W R/W R/W R/W

The FIFO control register (SCFCR) resets the quantity of data in the transmit and receive FIFO

registers, sets the trigger data quantity, and contains an enable bit for loop-back testing. SCFCR

can always be read and written to by the CPU. It is initialized to H'00 by a reset, by the module

standby function, and in standby mode.

Bits 7 and 6—Receive FIFO Data Trigger (RTRG1, RTRG0): Set the quantity of receive data

which sets the receive data full (RDF) flag in the serial status register (SCSSR). The RDF flag is

set to 1 when the quantity of receive data stored in the receive FIFO register (SCFRDR) exceeds

the set trigger number shown below.

Bit 7: RTRG1 Bit 6: RTRG0 Receive Trigger Number

0 0 1 (Initial value)

014

108

1114

Bits 5 and 4—Transmit FIFO Data Trigger (TTRG1, TTRG0): Set the quantity of remaining

transmit data which sets the transmit FIFO data register empty (TDFE) flag in the serial status

register (SCSSR). The TDFE flag is set to 1 when the quantity of transmit data in the transmit

FIFO data register (SCFTDR) becomes less than the set trigger number shown below.

Bit 5: TTRG1 Bit 4: TTRG0 Transmit Trigger Number

008 (8)

*

0 1 4 (12)

1 0 2 (14)

1 1 1 (15)

Note: * Initial value. Values in parentheses mean the number of empty bits in SCFTDR when the

TDFE flag is set to 1.