Rev. 5.00, 09/03, page 716 of 760

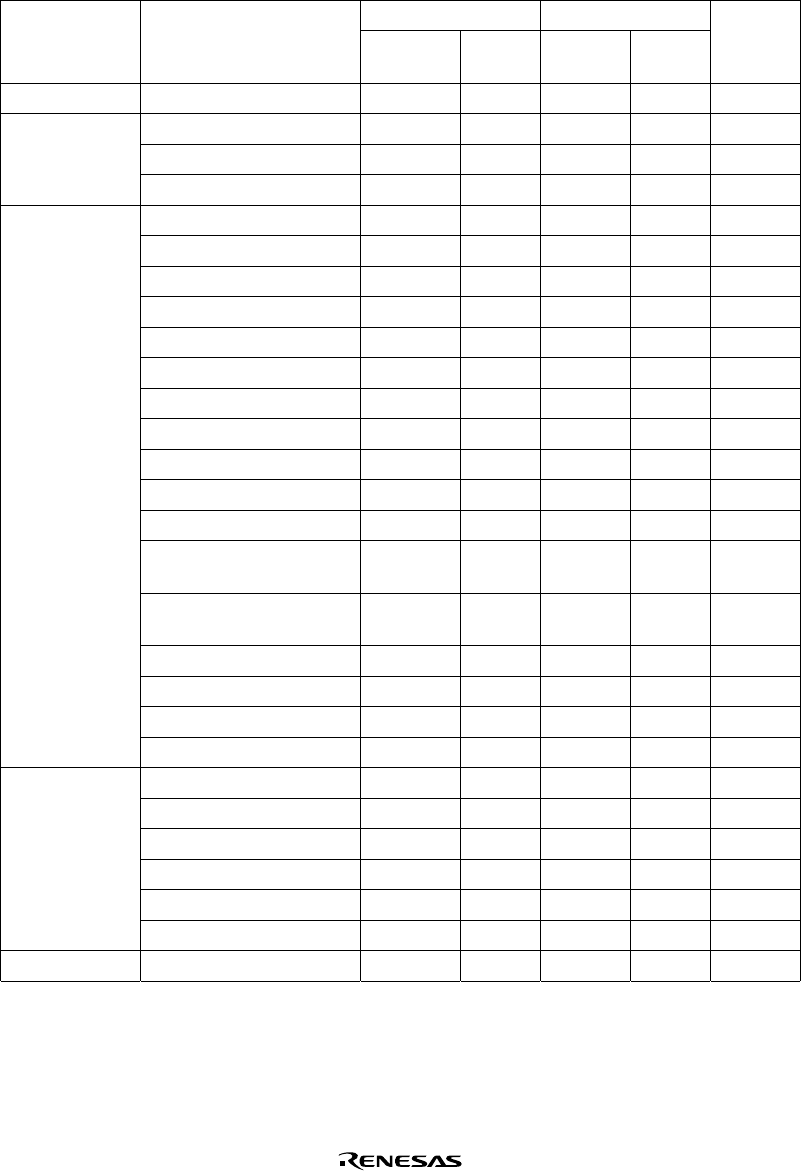

Reset Power-Down

Category Pin

Power-On

Reset

Manual

Reset

Standby Sleep

Bus

Released

Address bus A[25:0] Z O ZL

*

9

OZ

D[15:0] Z I Z IO Z

D[23:16]/PTA[7:0] Z IP

*

2

ZK

*

2

IOP

*

2

ZP

*

2

Data bus

D[31:24]/PTB[7:0] Z IP

*

2

ZK

*

2

IOP

*

2

ZP

*

2

CS0/MCS0 HOZH

*

10

OZ

CS[2:4]/PTK[0:2] H OP

*

2

ZH

*

10

K

*

2

OP

*

2

ZP

*

2

CS5/CE1A/PTK[3] H OP

*

2

ZH

*

10

K

*

2

OP

*

2

ZP

*

2

CS6/CE1B HOZH

*

10

OZ

BS/PTK[4] H OP

*

2

ZH

*

10

K

*

2

OP

*

2

ZP

*

2

RAS3L/PTJ[0] H OP

*

2

ZOK

*

3

OP

*

2

ZOP

*

3

RAS3U/PTE[2] V OP

*

2

ZOK

*

3

OP

*

2

ZOP

*

3

CASL/PTJ[2] H OP

*

2

ZOK

*

3

OP

*

2

ZOP

*

3

CASU/PTJ[3] H OP

*

2

ZOK

*

3

OP

*

2

ZOP

*

3

WE0/DQMLL H O ZH

*

10

OZ

WE1/DQMLU/WE HOZH

*

10

OZ

WE2/DQMUL/ICIORD/

PTK[6]

HOP

*

2

ZH

*

10

K

*

2

OP

*

2

ZP

*

2

WE3/DQMUU/ICIOWR/

PTK[7]

HOP

*

2

ZH

*

10

K

*

2

OP

*

2

ZP

*

2

RD/WR HOZH

*

10

OZ

RD HOZH

*

10

OZ

CKE/PTK[5] H OP

*

2

OK

*

2

OP

*

2

OP

*

2

Bus control

WAIT ZIZIZ

DREQ0/PTD[4] V ZI

*

6

ZII

DACK0/PTD[5] V OP

*

2

ZK

*

2

OP

*

2

OP

*

2

DRAK0/PTD[1] V OP

*

2

ZH

*

10

K

*

2

OP

*

2

OP

*

2

DREQ1/PTD[6] V ZI

*

6

ZII

DACK1/PTD[7] V OP

*

2

ZK

*

2

OP

*

2

OP

*

2

DMAC

DRAK1/PTD[0] V OP

*

2

ZH

*

10

K

*

2

OP

*

2

OP

*

2

Timer TCLK/PTH[7] V ZP IOP

*

4

IOP

*

4

IOP

*

4