Rev. 5.00, 09/03, page 731 of 760

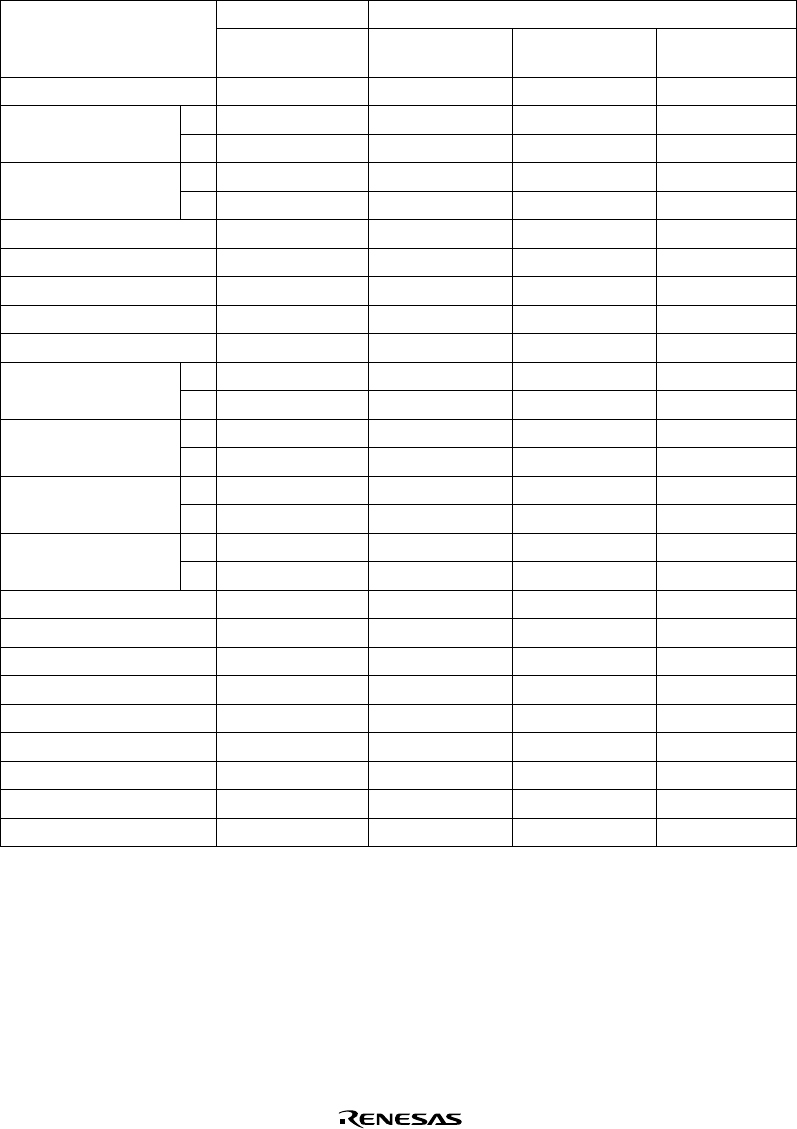

Table A.6 Pin States (Burst ROM/Big Endian)

8-Bit Bus Width 16-Bit Bus Width

Pin

Byte/Word/Long-

word Access

Byte Access

(Address 2n)

Byte Access

(Address 2n + 1)

Word/Longword

Access

CS6 to CS2, CS0 Enabled Enabled Enabled Enabled

R Low Low Low LowRD

W— ———

R High High High HighRD/WR

W— ———

BS Enabled Enabled Enabled Enabled

RAS3U/PTE[2] High High High High

RAS3L/PTJ[0] High High High High

CASL/PTJ[2] High High High High

CASU/PTJ[3] High High High High

R High High High HighWE0/DQMLL

W— ———

R High High High HighWE1/DQMLU/WE

W— ———

R High High High HighWE2/DQMUL/

ICIORD/PTK[6]

W— ———

R High High High HighWE3/DQMUU/

ICIOWR/PTK[7]

W— ———

CE2A/PTE[4] High High High High

CE2B/PTE[5] High High High High

CKE/PTK[5] Disabled Disabled Disabled Disabled

WAIT Enabled

*

1

Enabled

*

1

Enabled

*

1

Enabled

*

1

IOIS16/PTG[7] Disabled Disabled Disabled Disabled

A25 to A0 Address Address Address Address

D7 to D0 Valid data Invalid data Valid data Valid data

D15 to D8 High-Z

*

2

Valid data Invalid data Valid data

D31 to D16 High-Z

*

2

High-Z

*

2

High-Z

*

2

High-Z

*

2