Rev. 5.00, 09/03, page 552 of 760

5. TEND Flag and TE Bit Processing: The TEND flag is set to 1 during transmission of the stop

bit of the last data. Consequently, if the TE bit is cleared to 0 immediately after setting of the

TEND flag has been confirmed, the stop bit will be in the process of transmission and will not be

transmitted normally. Therefore, the TE bit should not be cleared to 0 for at least 0.5 serial clock

cycles (or 1.5 cycles if two stop bits are used) after setting of the TEND flag is confirmed.

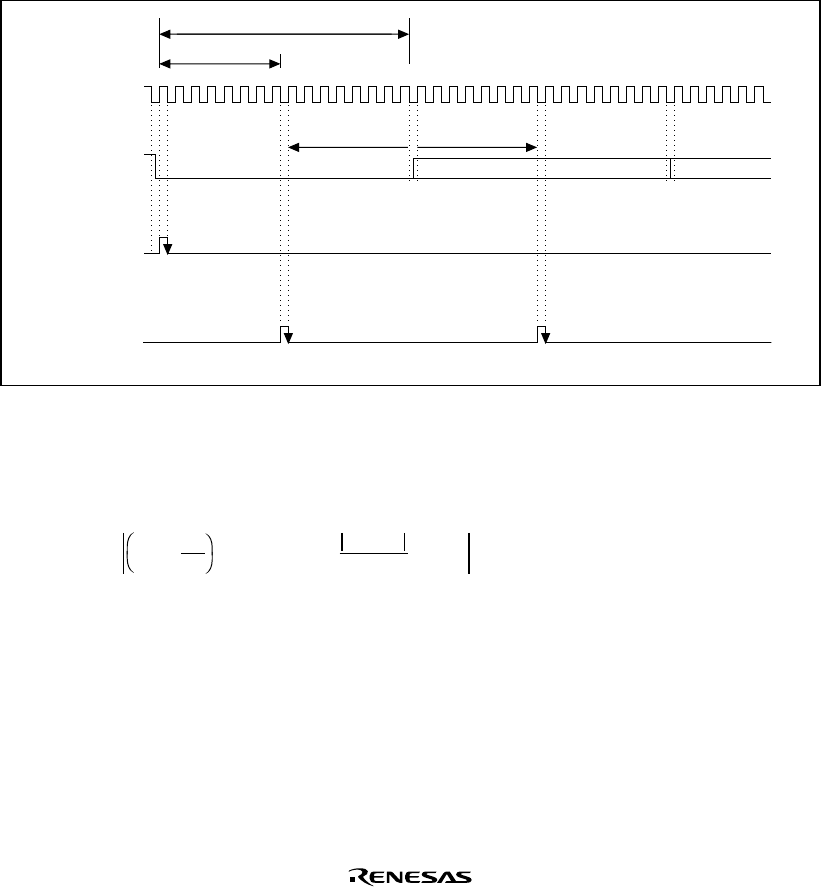

6. Receive Data Sampling Timing and Receive Margin: The SCIF operates on a base clock

with a frequency of 16 times the transfer rate. In reception, the SCIF synchronizes internally with

the fall of the start bit, which it samples on the base clock. Receive data is latched at the rising

edge of the eighth base clock pulse. The timing is shown in figure 16.13.

0 1 2 3 4 5 6 7 8 9 101112131415 0 1 2 3 4 5 6 7 8 9 101112131415 0 1 2 3 4 5

Base clock

Receive

data (RxD)

Synchro-

nization

sampling

timing

Data

sampling

timing

8 clocks

16 clocks

Start bit

−7.5 clocks

+7.5 clocks

D0 D1

Figure 16.13 Receive Data Sampling Timing in Asynchronous Mode

The receive margin in asynchronous mode can therefore be expressed as shown in equation 1.

Equation 1:

M = 0.5 −

1

2N

D − 0.5

N

− (L − 0.5) F −

(1 + F) × 100%

Where: M: Receive margin (%)

N: Ratio of clock frequency to bit rate (N = 16)

D: Clock duty cycle (D = 0 to 1.0)

L: Frame length (L = 9 to 12)

F: Absolute deviation of clock frequency

From equation 1, if F = 0 and D = 0.5, the receive margin is 46.875%, as given by equation 2.