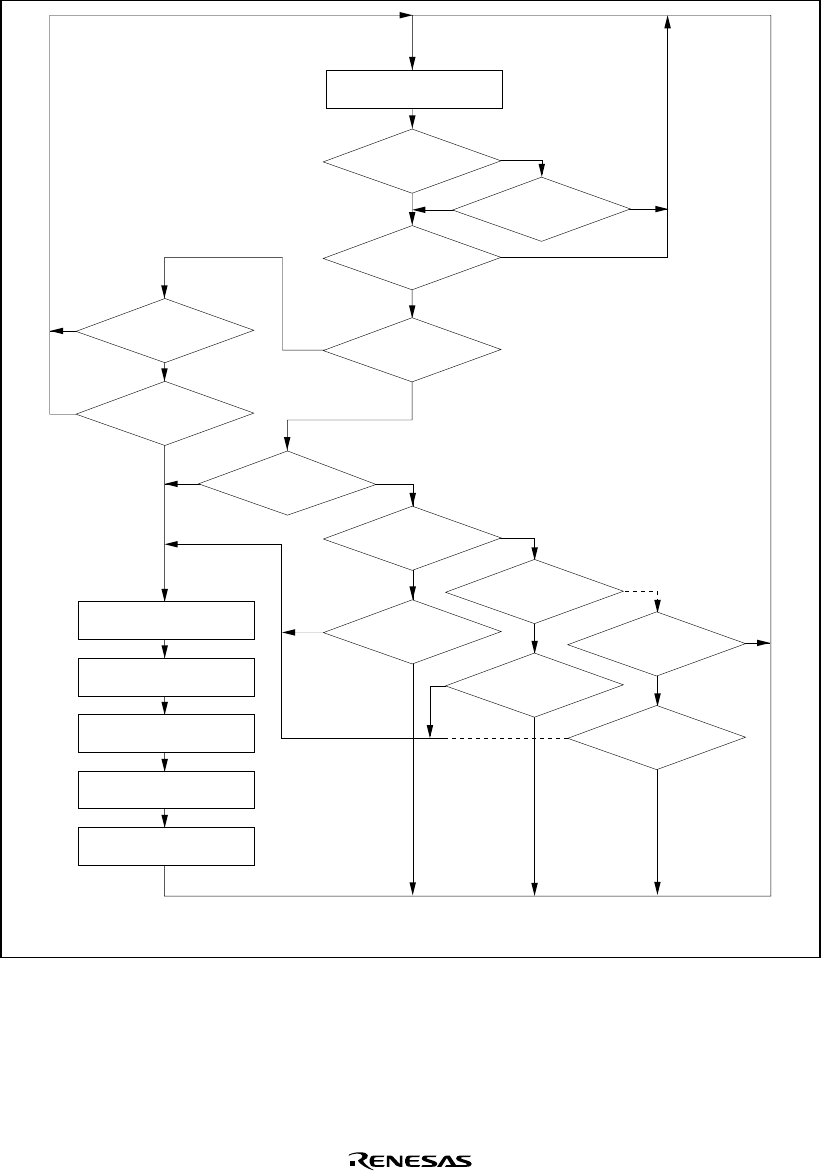

Rev. 5.00, 09/03, page 144 of 760

No

Yes

Yes

Yes

Yes

Yes

Yes

Yes

No

No

No

No

No

Level 15

interrupt?

I3−I0: Interrupt mask bits in status register (SR)

Program

execution state

ICR1.MAI = 1?

Interrupt

generated?

NMI = low?

SR.BL= 0

or sleep mode?

Yes

Yes

Yes

Yes

Yes

Yes

No

No

No

No

No

No

No

ICR1.BLMSK = 1?

NMI?

NMI?

IRQOUT = low

Set interrupt cause in

INTEVT, INTEVT2

Save SR to SSR;

save PC to SPC

Set BL/MD/RB

bits in SR to 1

Branch to exception

handler

I3−I0 level

14 or lower?

Level 14

interrupt?

I3−I0 level

13 or lower?

Level 1

interrupt?

I3−I0

level 0?

Figure 6.3 Interrupt Operation Flowchart