Rev. 5.00, 09/03, page 429 of 760

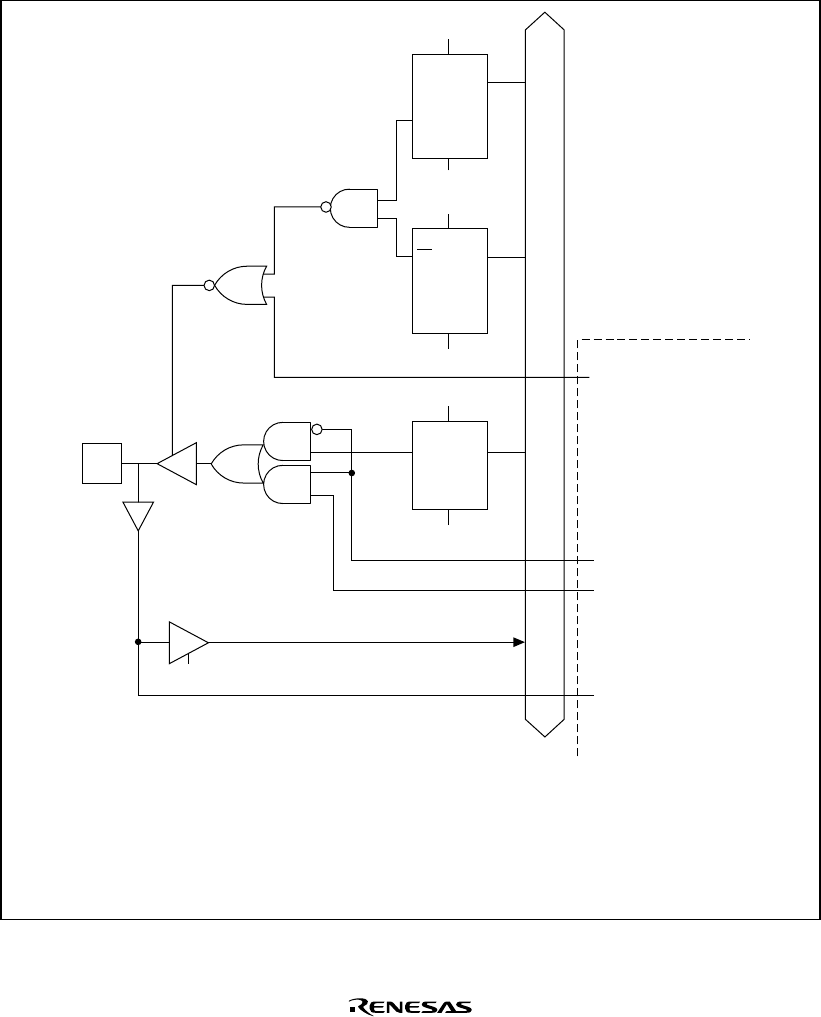

Figures 14.2, 14.3, and 14.4 show block diagrams of the SCI I/O port pins.

SCIF pin I/O and data control is performed by bits 11 to 8 of SCPCR and bits 5 and 4 of SCPDR.

For details, see section 14.2.8, SC Port Control Register (SCPCR)/SC Port Data Register

(SCPDR).

Internal data bus

Output enable

Clock input enable

SCI

Serial clock output

Serial clock input

R

SCP1MD0

PCRW

Reset

C

Q

Q

D

R

SCP1MD1

PCRW

Reset

C

QD

R

SCP1DT1

PDRW

Reset

SCPT[1]/SCK0

C

D

PDRW: SCPDR write

PDRR:

PCRW:

SCPDR read

SCPCR write

PDRR*

Note: *

Legend

When reading the SCK0 pin, clear the C/A bit in SCSMR and the CKE1 and CKE0

bits in SCSCR to 0, and set the SCP1MD1 bit in SCPCR to 1 (see section 14.2.8,

SC Port Control Register (SCPCR)/SC Port Data Register (SCPDR)).

Figure 14.2 SCPT[1]/SCK0 Pin