Rev. 5.00, 09/03, page 90 of 760

instruction or delay slot is accepted after execution of the delayed branch instruction. The delay

slot here refers either to the next instruction after a delayed unconditional branch instruction or to

the next instruction when a delayed conditional branch instruction is true.

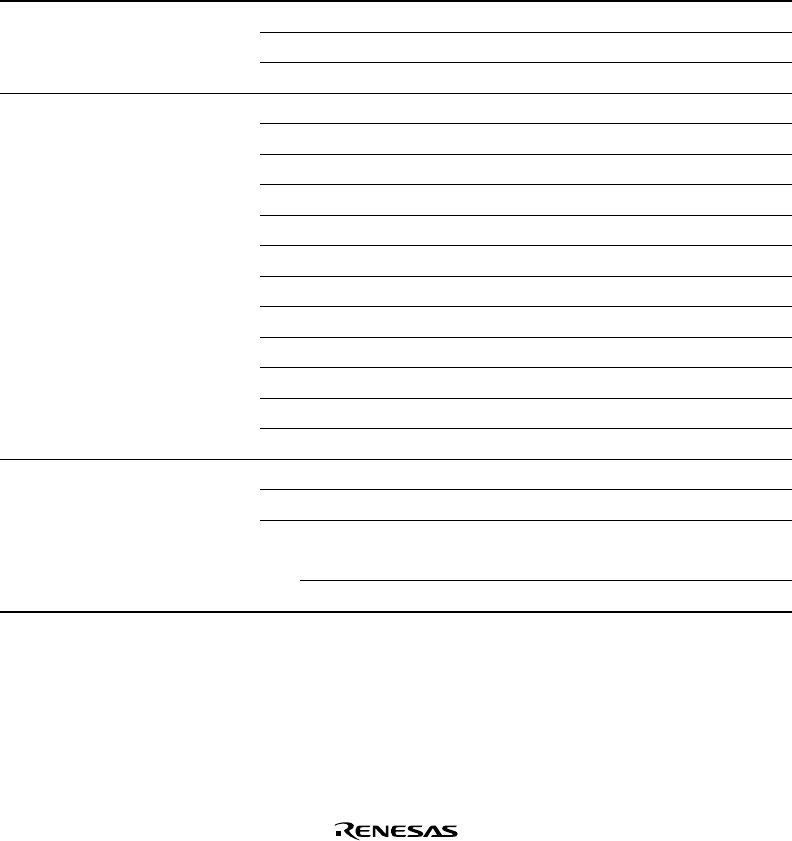

4.2.4 Exception Codes

Table 4.3 lists the exception codes written to the EXPEVT register (for reset or general

exceptions) or the INTEVT and INTEVT2 registers (for general interrupt requests) to identify

each specific exception event.

Table 4.3 Exception Codes

Exception Type Exception Event Exception Code

Reset Power-on reset H'000

Manual reset H'020

UDI reset H'000

General exception events TLB miss/invalid (read) H'040

TLB miss/invalid (write) H'060

Initial page write H'080

TLB protection violation (read) H'0A0

TLB protection violation (write) H'0C0

CPU address error (read) H'0E0

CPU address error (write) H'100

Unconditional trap (TRAPA instruction) H'160

Illegal general instruction exception H'180

Illegal slot instruction exception H'1A0

User breakpoint trap H'1E0

DMA address error H'5C0

General interrupt requests Nonmaskable interrupt H'1C0

UDI interrupt H'5E0

External hardware interrupts:

IRL3–IRL0

= 0000 H'200

IRL3–IRL0

= 0001 H'220