Rev. 5.00, 09/03, page 715 of 760

Appendix A Pin Functions

A.1 Pin States

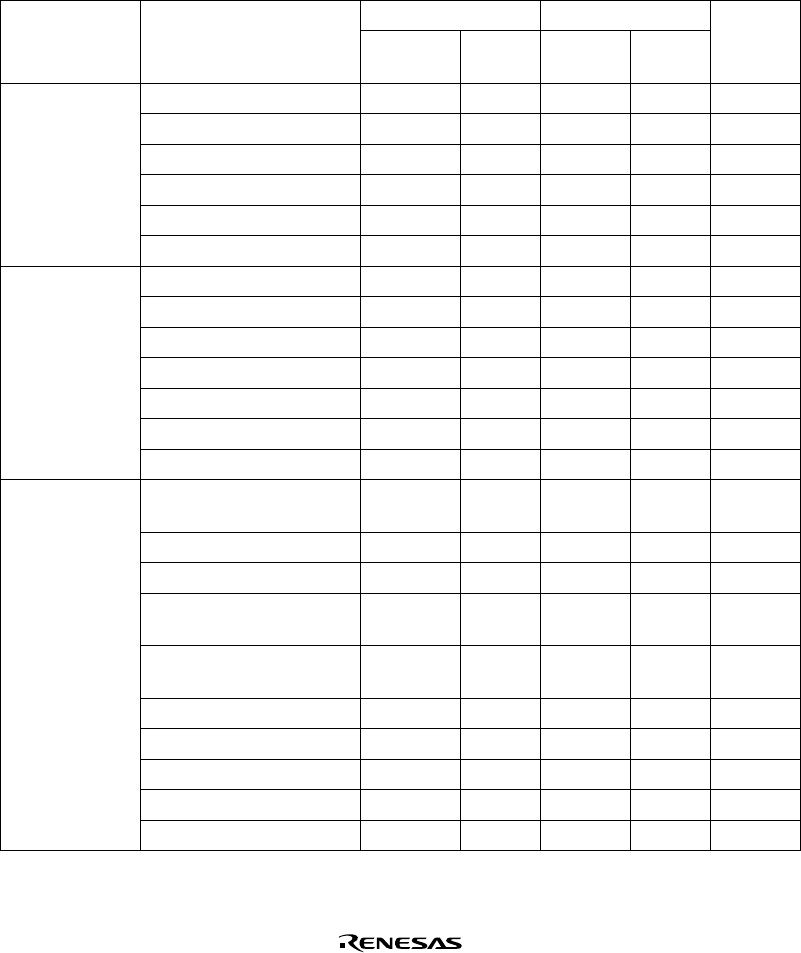

Table A.1 shows pin states during resets, power-down states, and the bus-released state.

Table A.1 Pin States during Resets, Power-Down States, and Bus-Released State

Reset Power-Down

Category Pin

Power-On

Reset

Manual

Reset

Standby Sleep

Bus

Released

EXTAL I IIII

XTAL O

*

1

O

*

1

O

*

1

O

*

1

O

*

1

CKIO IO

*

1

IO

*

1

IO

*

1

IO

*

1

IO

*

1

EXTAL2 I IIII

XTAL2 O OOOO

Clock

CAP1, CAP2 — ————

RESETP I IIII

RESETM I IIII

BREQ I IIII

BACK O OOOL

MD[5:0] I IIII

CA I IIII

System control

STATUS[1:0]/PTJ[7:6] O OP

*

2

OP

*

2

OP

*

2

OP

*

2

IRQ[3:0]/IRL[3:0]/

PTH[3:0]

V

*

7

IIII

IRQ[4]/ PTH[4] V

*

7

IIII

NMI I IIII

IRLS[3:0]/PTF[3:0]/

PINT[11:8]

VIIZII

MCS[7:0]/PTC[7:0]/

PINT[7:0]

VOP

*

2

ZH

*

10

K

*

2

OP

*

2

ZP

*

2

TCK/PTF[4]/PINT[12] IV I IZ I I

TDI/PTF[5]/PINT[13] IV I IZ I I

TMS/PTF[6]/PINT[14] IV I IZ I I

TRST/PTF[7]/PINT[15] IV I IZ I I

Interrupt

IRQOUT O OOOO