Rev. 5.00, 09/03, page 353 of 760

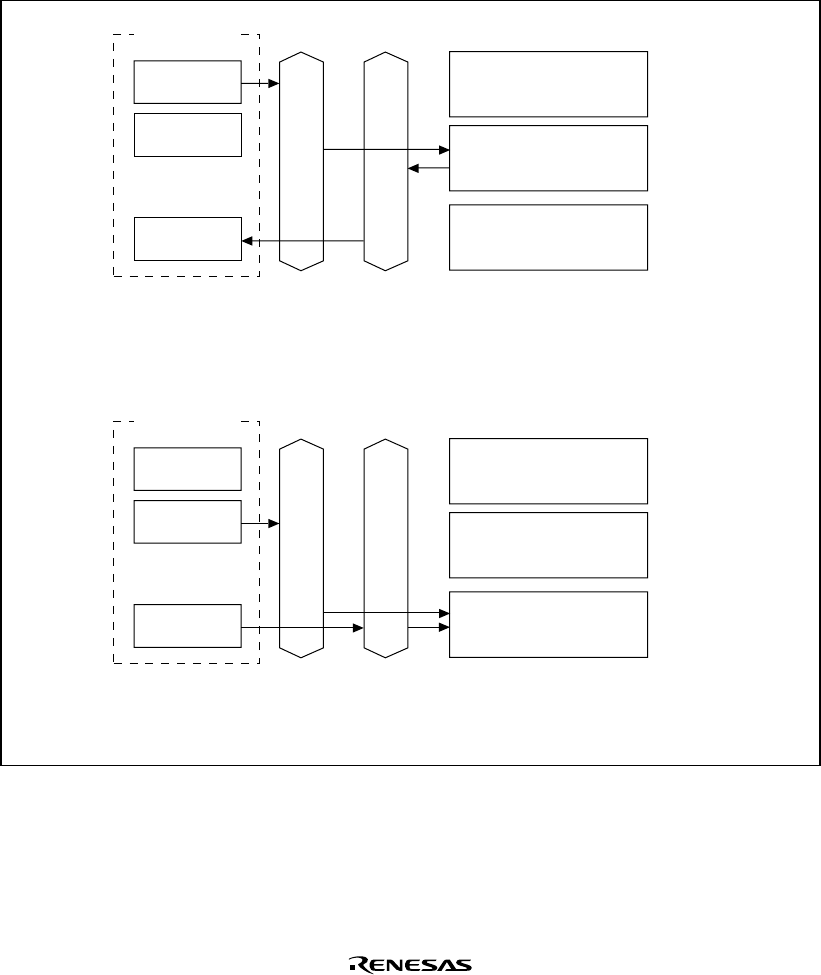

(1) In direct address transfer mode, DMA transfer requires two bus cycles because data is read

from the transfer source in a data read cycle and written to the transfer destination in a

data write cycle. At this time, transfer data is temporarily stored in the DMAC. In the

transfer between external memories as shown in figure 11.5, data is read to the DMAC

from one external memory in a data read cycle, and then that data is written to the other

external memory in a write cycle. Figure 11.6 shows an example of the timing at this

time.

Data buffer

Address bus

Data bus

Address bus

Data bus

Memory

Transfer source

module

Transfer destination

module

Memory

Transfer source

module

Transfer destination

module

SAR

DAR

Data buffer

SAR

DAR

The SAR value is an address, data is read from the transfer source module,

and the data is temporarily stored in the DMAC.

First bus cycle

Second bus cycle

The DAR value is an address, and the value stored in the data buffer in the

DMAC is written to the transfer destination module.

DMAC

DMAC

Figure 11.5 Operation of Direct Address Mode in Dual Address Mode