Rev. 5.00, 09/03, page 167 of 760

7.2.11 Branch Source Register (BRSR)

BRSR is a 32-bit read register. BRSR stores the last fetched address before branch and the pointer

(3 bits) which indicates the number of cycles from fetch to execution for the last executed

instruction. BRSR has the flag bit that is set to 1 when branch occurs. This flag bit is cleared to 0,

when BRSR is read and also initialized by power-on resets or manual resets. Other bits are not

initialized by reset. Eight BRSR registers have queue structure and a stored register is shifted

every branch.

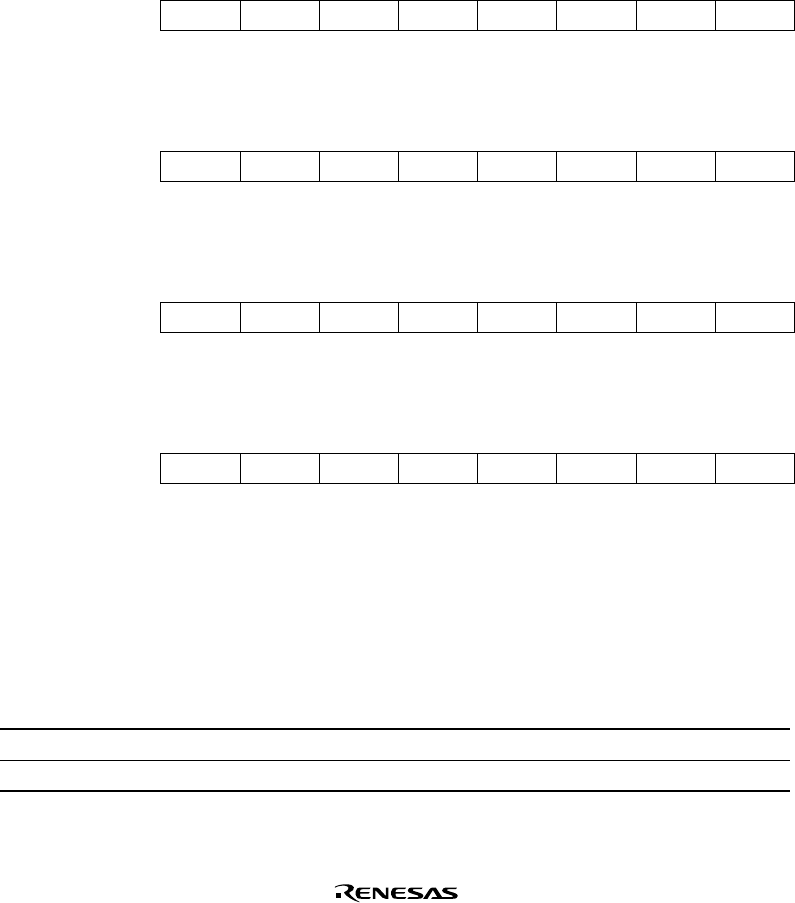

Bit: 31 30 29 28 27 26 25 24

SVF PID2 PID1 PID0 BSA27 BSA26 BSA25 BSA24

Initial value: 0 *******

R/W:RRRRRRRR

Bit: 23 22 21 20 19 18 17 16

BSA23 BSA22 BSA21 BSA20 BSA19 BSA18 BSA17 BSA16

Initial value: ********

R/W:RRRRRRRR

Bit: 15 14 13 12 11 10 9 8

BSA15 BSA14 BSA13 BSA12 BSA11 BSA10 BSA9 BSA8

Initial value: ********

R/W:RRRRRRRR

Bit:76543210

BSA7 BSA6 BSA5 BSA4 BSA3 BSA2 BSA1 BSA0

Initial value: ********

R/W:RRRRRRRR

Note: * Undefined value

Bit 31—BRSR Valid Flag (SVF): Indicates whether the address and the pointer by which the

branch source address can be calculated. When a branch source address is fetched, this flag is set

to 1. This flag is cleared to 0 in reading BRSR.

Bit 31: SVF Description

0 The value of BRSR register is invalid

1 The value of BRSR register is valid