Rev. 5.00, 09/03, page 249 of 760

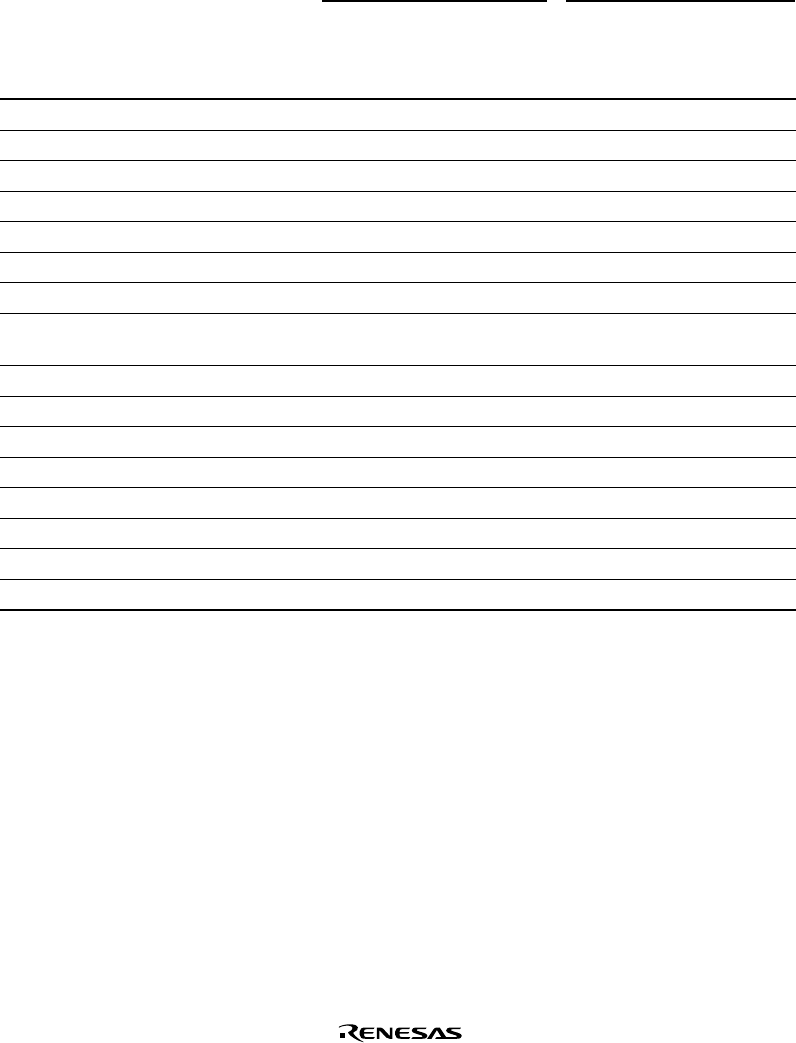

Bit 15—Area 6 Wait Control (A6W3): Specifies the number of inserted wait states for area 6

combined with bits A6W2–A6W0 in WCR2. Also specifies the number of transfer states in burst

transfer. Clear this bit to 0 when area 6 is not set to PCMCIA.

First Cycle Burst Cycle

A6W3 A6W2 A6W1 A6W0

Inserted Wait

States W

WW

WA

AA

AI

II

IT

TT

T Pin

Number of

States per

One-data

Transfer W

WW

WA

AA

AI

II

IT

TT

T Pin

0 0 0 0 0 Ignored 2 Enabled

0 0 0 1 1 Enabled 2 Enabled

0 0 1 0 2 Enabled 3 Enabled

0 0 1 1 3 Enabled 4 Enabled

0 1 0 0 4 Enabled 5 Enabled

0 1 0 1 6 Enabled 7 Enabled

0 1 1 0 8 Enabled 9 Enabled

011110

(Initial value)

Enabled 11 Enabled

1 0 0 0 12 Enabled 13 Enabled

1 0 0 1 14 Enabled 15 Enabled

1 0 1 0 18 Enabled 19 Enabled

1 0 1 1 22 Enabled 23 Enabled

1 1 0 0 26 Enabled 27 Enabled

1 1 0 1 30 Enabled 31 Enabled

1 1 1 0 34 Enabled 35 Enabled

1 1 1 1 38 Enabled 39 Enabled

Bit 14—Area 5 Wait Control (A5W3): Specifies the number of inserted wait states for area 5

combined with bits A5W2–A5W0 in WCR2. Also specifies the number of transfer states in burst

transfer. Clear this bit to 0 when area 5 is not set to PCMCIA.

The relationship between the set value and the number of waits is the same as for A6W3.

Bits 13 and 12—Reserved: These bits are always read as 0. The write value should always be 0.