Rev. 5.00, 09/03, page 373 of 760

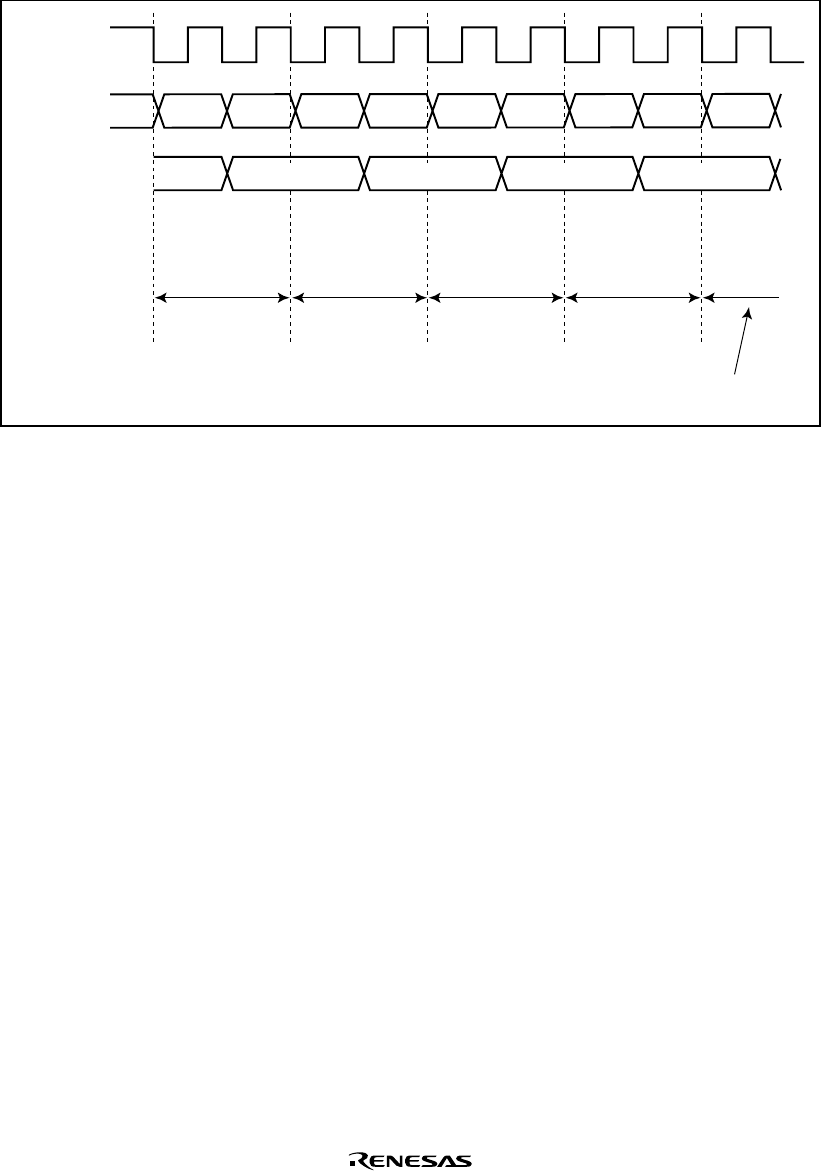

CK

Internal

address bus

Internal

data bus

SAR2 DAR2 DAR2 DAR2 DAR2SAR2+2 SAR2+4 SAR2+6 SAR2

SAR2 data SAR2+2 data SAR2+4 data SAR2+6 data

First transfer on

channel 2

Second transfer Third transfer Fourth transfer Fifth transfe

r

SAR2 output

DAR2 output

SAR2+2 output

DAR2 output

SAR2+4 output

DAR2 output

SAR2+6 output

DAR2 output

SAR2 reload

SAR2 output

DAR2 output

Figure 11.23 Timing Chart of Source Address Reload Function

The reload function can be executed with a transfer data size of 8, 16, or 32 bits.

DMATCR2, which specifies the transfer count, decrements 1 each time a transfer ends regardless

of whether the reload function is on or off. Consequently, a multiple of four must be specified in

DMATCR2 when the reload function is on. Operation is not guaranteed if other values are

specified.

The counter that counts the execution of four transfers for the address reload function is reset by

clearing the DME bit in DMAOR or the DE bit in CHCR2, by setting the transfer end flag (TE bit

in CHCR2), by DMAC address error, and by NMI input, as well as by a reset, but the SAR2,

DAR2, and DMATCR2 registers are not reset. Therefore, if these sources are generated, there will

be a mix of an initialized counter and uninitialized registers in the DMAC, and a malfunction will

be caused by restarting the DMAC in that state. Consequently, if one of these sources other than

setting of the TE bit occurs during use of the address reload function, set SAR2, DAR2, and

DMATCR2 again.