Rev. 5.00, 09/03, page 512 of 760

16.1.2 Block Diagram

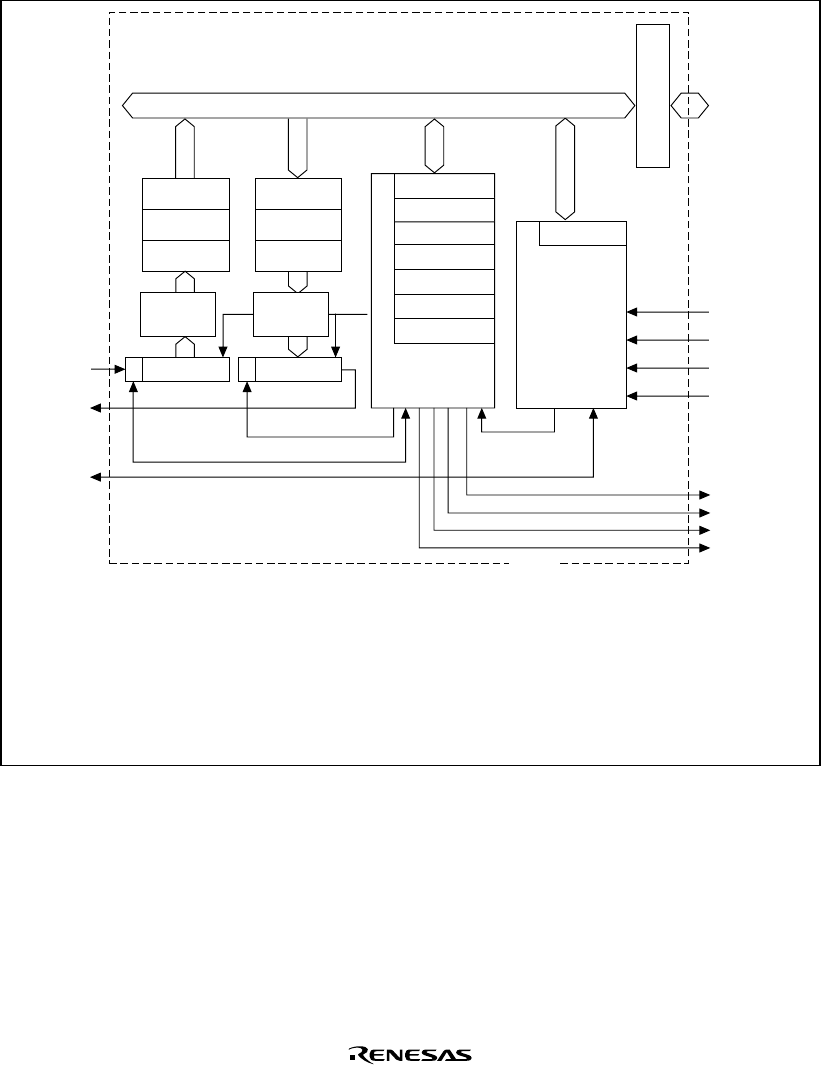

Figure 16.1 shows a block diagram of the SCIF.

RxD

TxD

SCK

SCIF

SCBRR

SCSSR2

SCSCR2

SCFTDR2

SCTSR

SCFRDR2

(16(16

stages)stages)

SCRSR

SCSMR2

SCFDR2

SCFCR2

SCPCR

SCFDR

Parity generation

Parity check

Clock

External clock

Module data bus

Internal

data bu

s

Pφ

Pφ/4

Pφ/16

Pφ/64

TXI

TEI

RXI

BRI

Bus interface

Baud rate

generator

Transmit/

receive

control

SCRSR:

SCFRDR2:

SCTSR:

SCFTDR2:

SCSMR2:

SCSCR2:

Legend

Receive shift register

Receive FIFO data register 2

Transmit shift register

Transmit FIFO data register 2

Serial mode register 2

Serial control register 2

SCSSR2:

SCBRR2:

SCFCR2:

SCFDR2:

SCPDR:

SCPCR:

Serial status register 2

Bit rate register 2

FIFO control register 2

FIFO data count register 2

Port SC data register

Port SC control register

Transmit

buffer

Receive

buffer

Figure 16.1 Block Diagram of SCIF