Rev. 5.00, 09/03, page 688 of 760

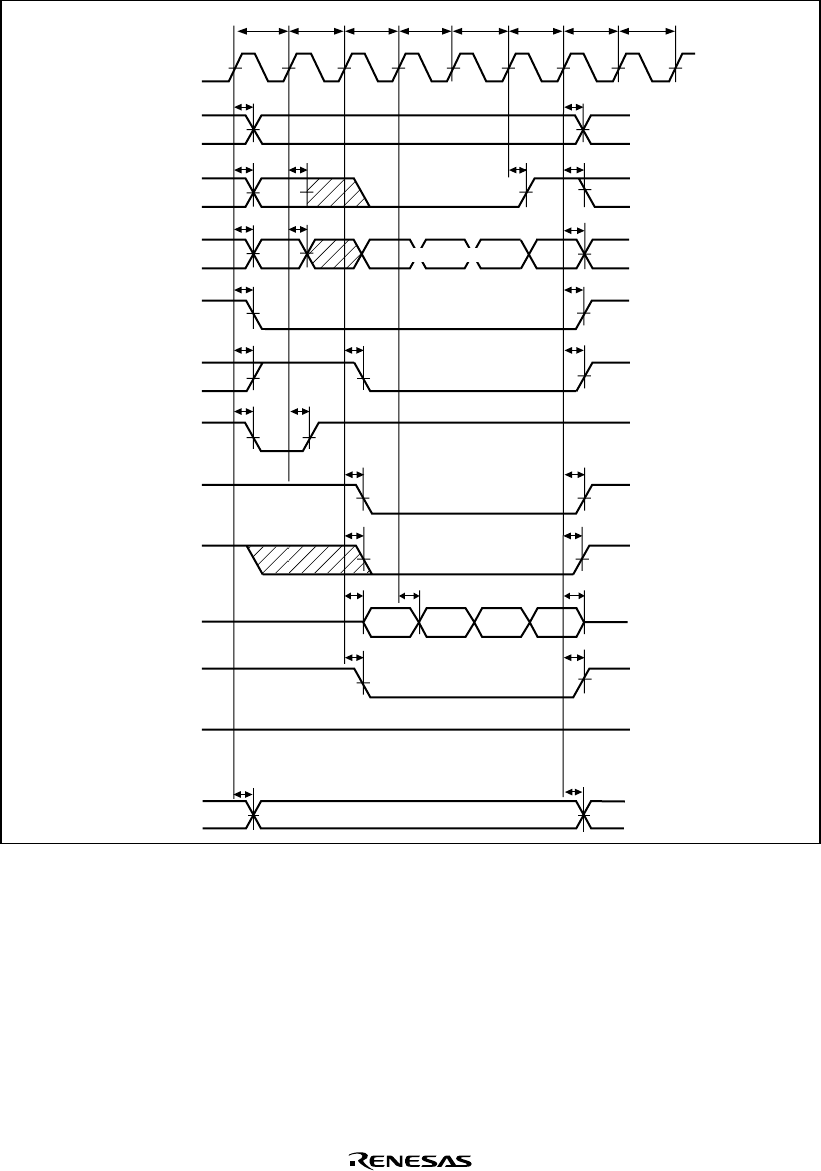

CKIO

A12 or A10

RD/WR

CSn

RAS

CAS

BS

DQMxx

CKE

(High)

A25 to A16

A15 to A0

Tr Trw Tc1 Tc2 Tc3

Td4 (Trwl) (Tpc)

D31 to D0

Row address

Row

address

Write A

command

Write command

Row

address

Column address (1-4)

tAD tAD

tAD tAD tAD tAD

tAD

tAD tAD

tCSD3 tCSD3

tRWD tRWD tRWD

tRASD2

tDQMD

tBSD tBSD

tWDD2 tWDD2

tWDH2

tDQMD

tRASD2

tCASD2 tCASD2

t

DAKD1

t

DAKD1

DACKn

Figure 23.29 Synchronous DRAM Write Bus Cycle (Burst Mode (Single Write ×

××

× 4),

RCD =

==

= 1, TPC =

==

= 0, TRWL = 0)