Rev. 5.00, 09/03, page 150 of 760

7.1.2 Block Diagram

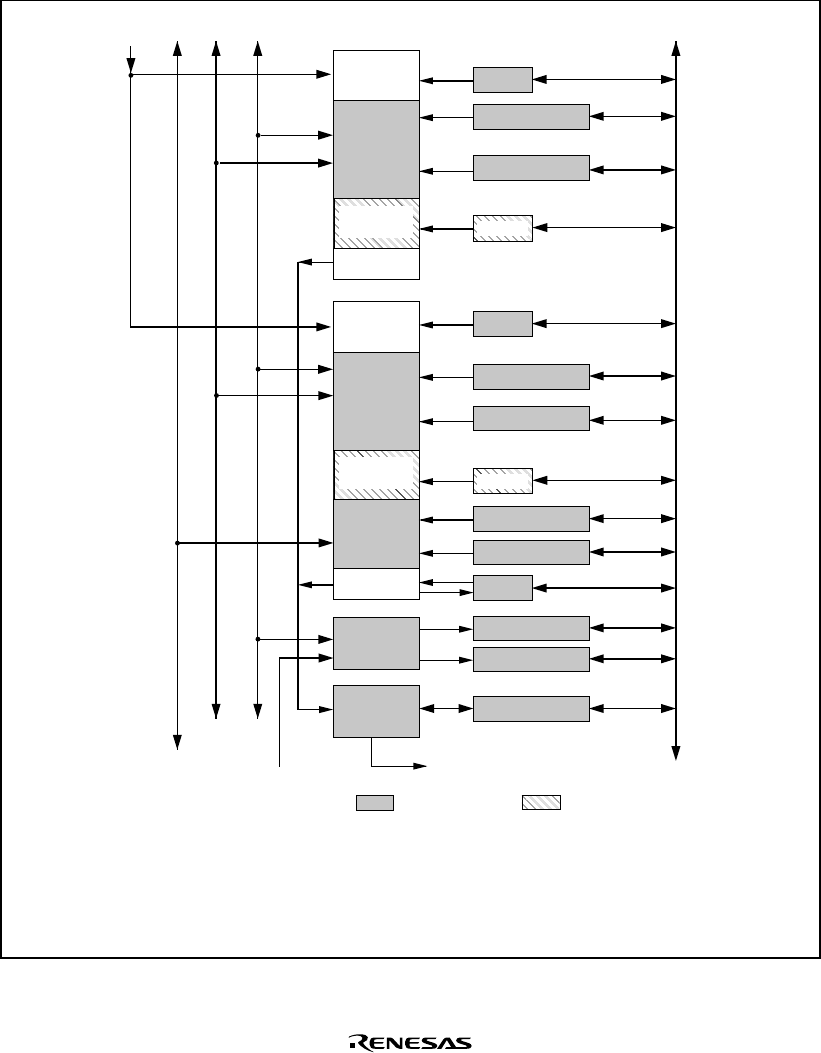

Figure 7.1 shows a block diagram of the UBC.

BBRA

BARA

BAMRA

BASRA

ASID

comparator

CPU state

signals

IAB LAB MDB

Access

comparator

Address

comparator

Channel A

ASID

comparator

Access

comparator

Address

comparator

Data

comparator

PC Trace

CONTROL

Channel B

BBRB

BETR

BARB

BAMRB

BASRB

BDRB

BDMRB

BRSR

BRDR

BRCR

User break request

UBC Location CCN Location

LDB/IDB/

XDB/YDB

A

ccess

Control

Legend

BBRA: Break bus cycle register A

BARA: Break address register A

BAMRA: Break address mask register A

BASRA: Break ASID register A

BBRB: Break bus cycle register B

BARB: Break address register B

BAMRB: Break address mask register B

BASRB: Break ASID register B

BDRB: Break data register B

BDMRB: Break data mask register B

BETR: Break execution times registe

r

BRSR: Branch source register

BRDR: Branch destination register

BRCR: Break control register

Figure 7.1 Block Diagram of User Break Controller