Rev. 5.00, 09/03, page 118 of 760

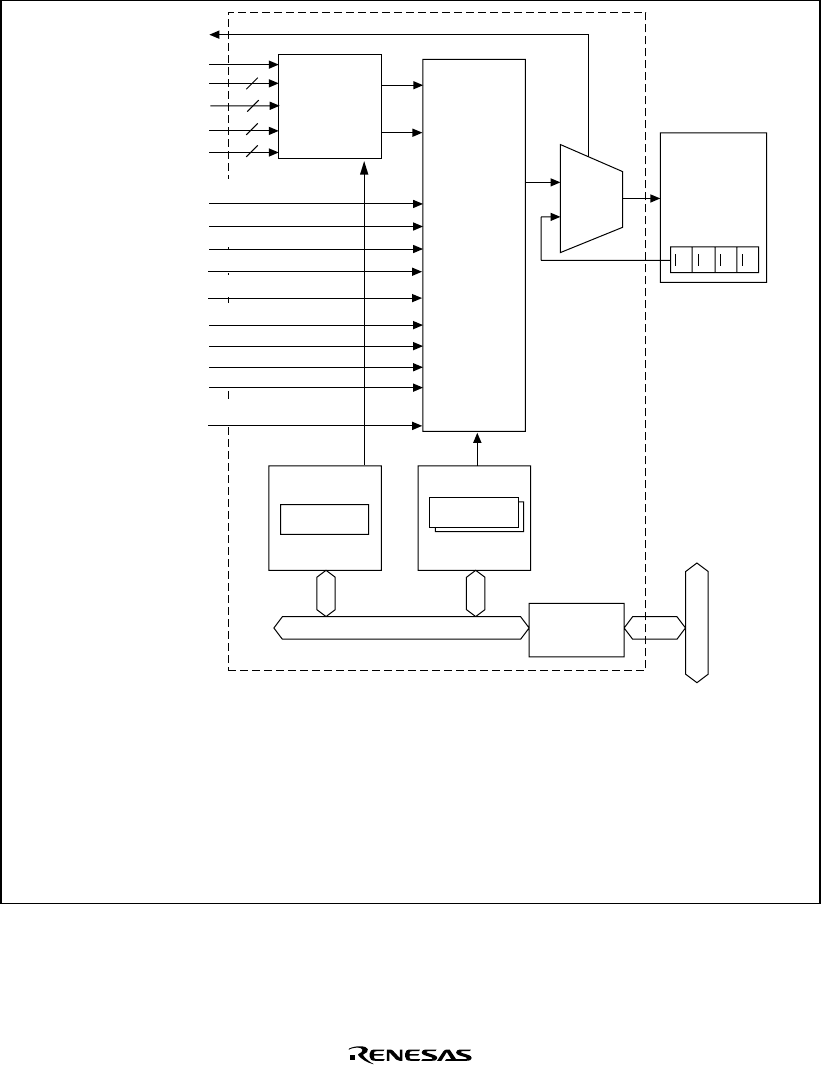

6.1.2 Block Diagram

Figure 6.1 shows a block diagram of the INTC.

REF

IrDA

DMAC

ICR

Input/output

control

Com-

parator

Priority

identifier

3

4

6

16

Interrupt

request

SR

IPRA–IPRE

IRL3–IRL0

NMI

IRQ0–IRQ5

PINT0–PINT15

IRQOUT

: Timer unit

: Realtime clock unit

: Serial communication interface

: Serial communication interface (with IrDA)

: Serial communication interface (with FIFO)

: Watchdog timer

: Refresh requests in the bus state controller

: Interrupt control register

: Interrupt priority registers A−E

: Status register

: Direct memory access controller

: Analog-to-digital converter

: User-debugging interface

Legend

TMU

RTC

SCI

IrDA

SCIF

WDT

REF

ICR

IPRA–IPRE

SR

DMAC

A

DC

UDI

(Interrupt request)

SCIF

TMU

(Interrupt request)

(Interrupt request/

IPR

CPU

Internal bus

Bus

interface

2 1 0

(Interrupt request)

(Interrupt request)

RTC

WDT

(Interrupt request)

(Interrupt request)

IRLS3–IRLS0

4

SCI

(Interrupt request)

ADC

(Interrupt request)

INTC

UDI

(Interrupt request)

refresh request)

Figure 6.1 Block Diagram of INTC