Rev. 5.00, 09/03, page 362 of 760

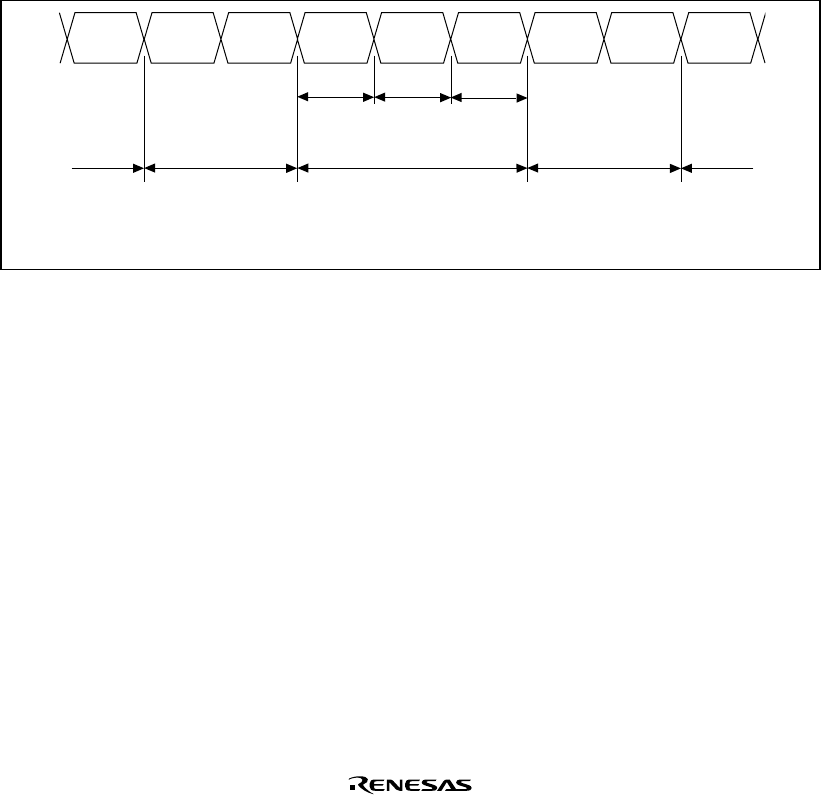

Bus Mode and Channel Priority Order: When, for example, channel 1 is transferring in burst

mode and there is a transfer request to channel 0, which has higher priority, the channel 0 transfer

will begin immediately.

At this time, if the priority is set in the fixed mode (CH0 > CH1), the channel 1 transfer will

continue when the channel 0 transfer has completely finished, even if channel 0 is operating in

cycle-steal mode or burst mode.

If the priority is set in round-robin mode, channel 1 will begin operating again after channel 0

completes the transfer of one transfer unit, even if channel 0 is in cycle-steal mode or burst mode.

The bus will then switch between the two in the order channel 1, channel 0, channel 1, channel 0.

Even if the priority is set in fixed mode or in round-robin mode, the bus will not be given to the

CPU since channel 1 is in burst mode. This example is illustrated in figure 11.14.

CPU

DMAC

CH1

DMAC

CH1

DMAC

CH0

DMAC

CH1

DMAC

CH0

DMAC

CH1

DMAC

CH1

CPU

CH0 CH1 CH0

Round-robin mode in

DMAC CH0 and CH1

DMAC CH1

Burst mode

CPUCPU

Priority: Round-robin mode

CH0: Cycle-steal mode

CH1: Burst mode

DMAC CH1

Burst mode

Figure 11.14 Bus State when Multiple Channels Are Operating