Rev. 5.00, 09/03, page 698 of 760

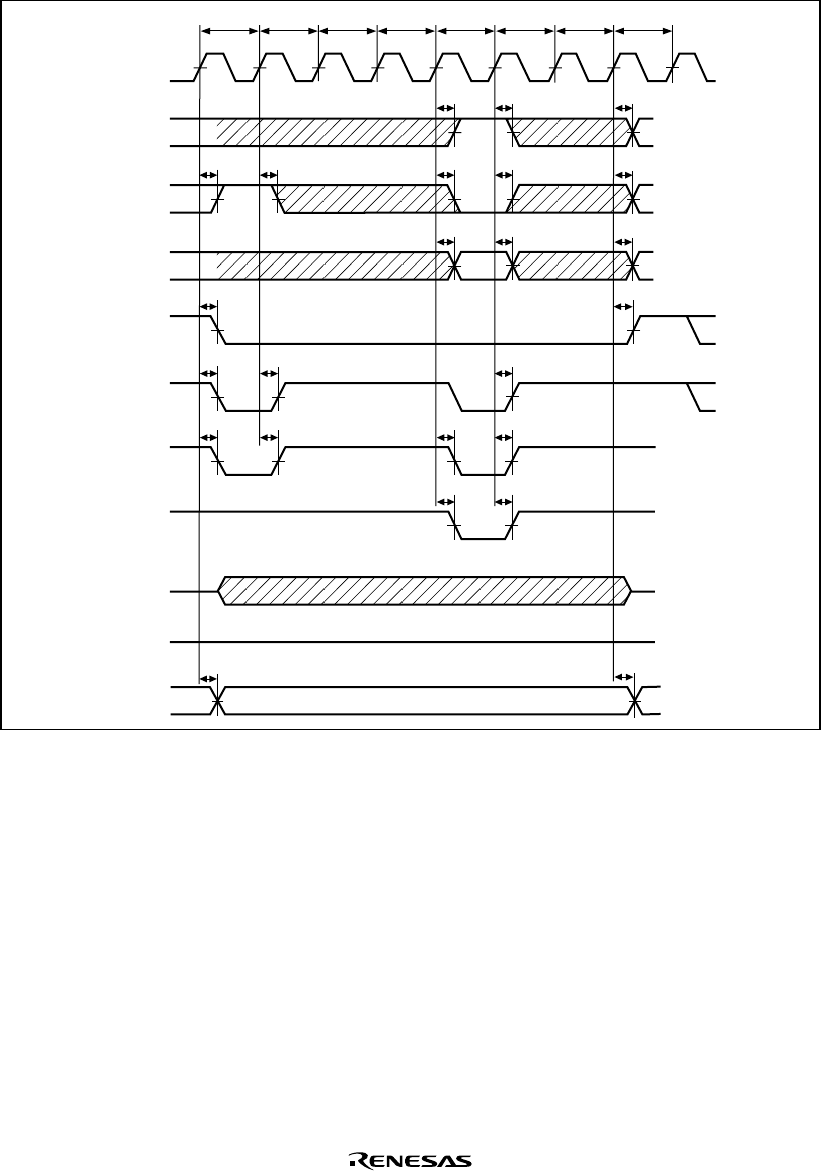

CKIO

A12 or A10

RD/WR

CSn

RAS

CASxx

D31 to D0

A13 or A11

A11 to A2

or A9 to A2

TRp1

TRp2 TRp3 TRp4 TMw1 TMw2 TMw3 TMw4

(High)

CKE

tAD tAD

tAD

tAD tAD

tAD

tAD

tAD

tAD tAD

tAD

tCSD3tCSD3

tRWDtRWDtRWD

tRASD2tRASD2tRASD2tRASD2

tCASD2tCASD2

t

DAKD1

t

DAKD1

DACKn

Figure 23.39 Synchronous DRAM Mode Register Write Cycle