Rev. 5.00, 09/03, page 96 of 760

• TLB invalid exception

Conditions: Comparison of TLB addresses shows address match but the TLB entry valid

bit (V) is 0.

Operations: The virtual address (32 bits) that caused the exception is set in TEA and the

corresponding virtual page number (22 bits) is set in PTEH (31–10). The ASID of PTEH

indicates the ASID at the time the exception occurred. The way that generated the

exception is set in the RC bits in MMUCR.

PC and SR of the instruction that generated the exception are saved to SPC and SSR,

respectively. If the exception occurred during a read, H'040 is set in EXPEVT; if the exception

occurred during a write, H'060 is set in EXPEVT. The BL, MD, and RB bits in SR are set to 1

and a branch occurs to PC = VBR + H'0100.

• Initial page write exception

Conditions: A hit occurred to the TLB for a store access, but the TLB entry data bit (D) is

0.

This occurs for initial writes to the page registered by the load.

Operations: The virtual address (32 bits) that caused the exception is set in TEA and the

corresponding virtual page number (22 bits) is set in PTEH (31–10). The ASID of PTEH

indicates the ASID at the time the exception occurred. The way that generated the

exception is set in the RC bit in MMUCR.

PC and SR of the instruction that generated the exception are saved to SPC and SSR,

respectively. H'080 is set in EXPEVT. The BL, MD, and RB bits in SR are set to 1 and a

branch occurs to PC = VBR + H'0100.

• TLB protection exception

Conditions: When a hit access violates the TLB protection information (PR bits) shown

below:

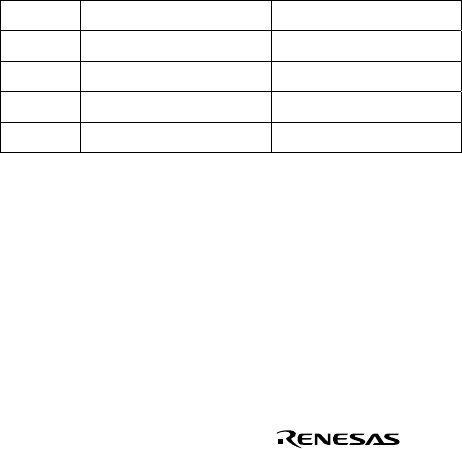

PR Privileged mode User mode

00 Only read enabled No access

01 Read/write enabled No access

10 Only read enabled Only read enabled

11 Read/write enabled Read/write enabled

Operations: The virtual address (32 bits) that caused the exception is set in TEA and the

corresponding virtual page number (22 bits) is set in PTEH (31–10). The ASID of PTEH

indicates the ASID at the time the exception occurred. The way that generated the

exception is set in the RC bits in MMUCR.

PC and SR of the instruction that generated the exception are saved to SPC and SSR,

respectively. If the exception occurred during a read, H'0A0 is set in EXPEVT; if the exception

occurred during a write, H'0C0 is set in EXPEVT. The BL, MD, and RB bits in SR are set to 1

and a branch occurs to PC = VBR + H'0100.