Rev. 5.00, 09/03, page 14 of 760

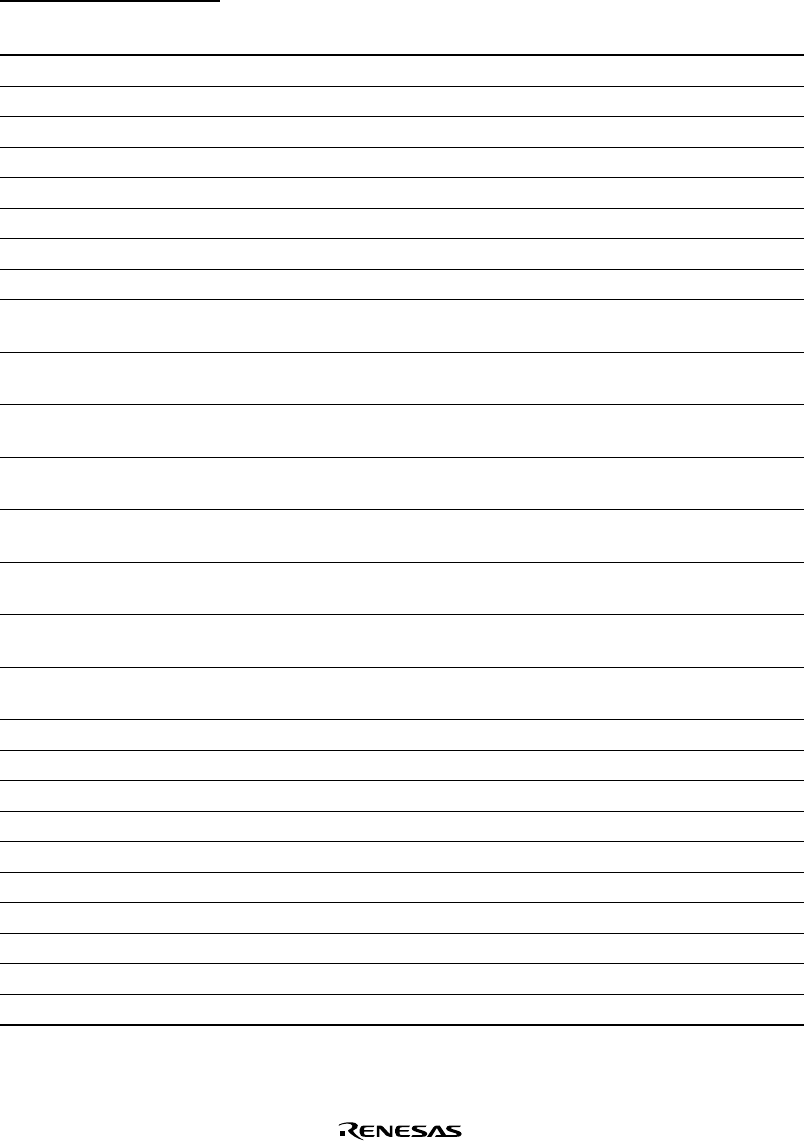

Number of Pins

FP-208C

FP-208E BP-240A Pin Name I/O Description

130 L17 AUDATA[3]/PTG[3] I/O / I AUD data / input port G

131 K18 AUDATA[2]/PTG[2] I/O/I AUD data / input port G

132 K17 Vss — Power supply (0 V)

— K16 Vss — Power supply (0 V)

133 K19 AUDATA[1]/PTG[1] I/O / I AUD data / input port G

134 J17 Vcc — Power supply (

*

3

)

— J16 Vcc — Power supply (

*

3

)

135 J18 AUDATA[0]/PTG[0] I/O / I AUD data / input port G

136 J19 TRST/PTF[7]/PINT[15] I Test reset / input port F / port

interrupt

137 H16 TMS/PTF[6]/PINT[14] I Test mode switch / input port F /

port interrupt

138 H17 TDI/PTF[5]/PINT[13] I Test data input / input port F / port

interrupt

139 H18 TCK/PTF[4]/PNT[12] I Test clock / input port F / port

interrupt

140 H19 IRLS3/PTF[3]/

PINT[11]

I External interrupt request / input

port F / port interrupt

141 G16 IRLS2/PTF[2]/

PINT[10]

I External interrupt request / input

port F / port interrupt

142 G17 IRLS1/PTF[1]/PINT[9] I External interrupt request / input

port F / port interrupt

143 G18 IRLS0/PTF[0]/PINT[8] I External interrupt request / input

port F / port interrupt

144 G19 MD0 I Clock mode setting

145 F16 Vcc-PLL1

*

2

— PLL1 power supply (

*

3

)

146 F17 CAP1 — PLL1 external capacitance pin

147 F18 Vss-PLL1

*

2

— PLL1 power supply (0 V)

148 F19 Vss-PLL2

*

2

— PLL2 power supply (0 V)

149 E16 CAP2 — PLL2 external capacitance pin

150 E17 Vcc-PLL2

*

2

— PLL2 power supply (

*

3

)

151 D16 AUDCK/PTH[6] I AUD clock / input port H

152 E19 Vss — Power supply (0 V)

153 D17 Vss — Power supply (0 V)