Rev. 5.00, 09/03, page 706 of 760

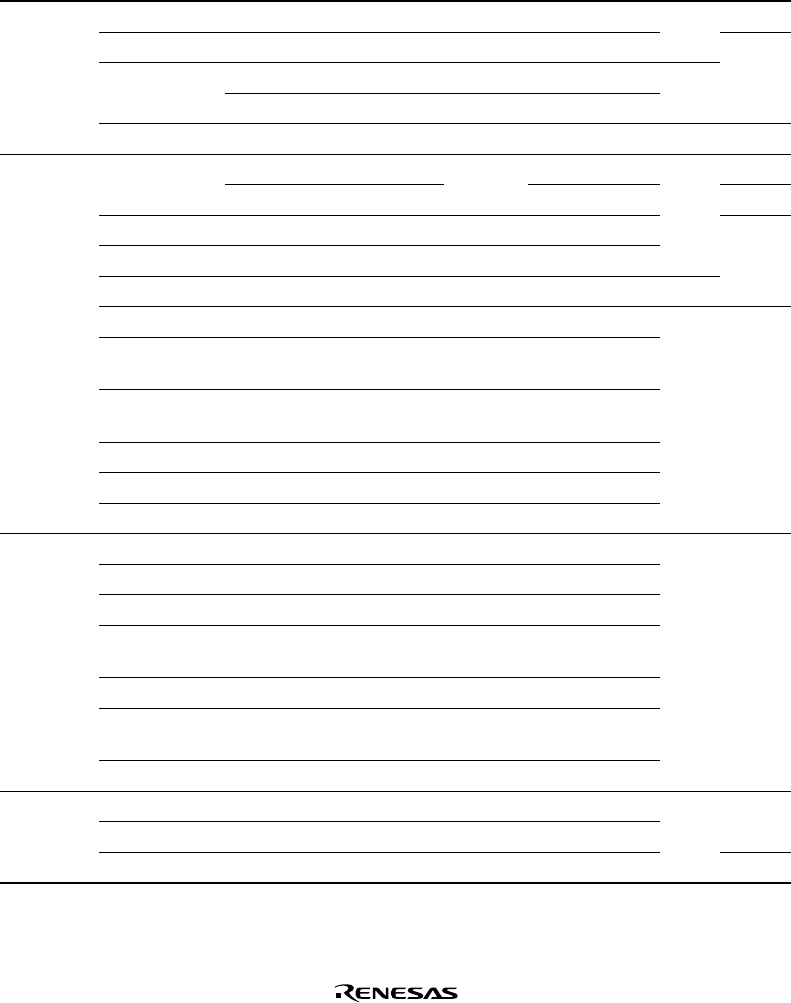

23.3.8 Peripheral Module Signal Timing

Table 23.8 Peripheral Module Signal Timing

VccQ = 3.3 ± 0.3 V, Vcc = 1.55 to 2.15 V, AVcc = 3.3 ± 0.3 V, Ta = –20 to 75°C

Module Item Symbol Min Max Unit Figure

Timer input setup time t

TCLKS

15 — ns 23.47TMU,

RTC

Timer clock input setup time t

TCKS

15 — 23.48

Edge specification t

TCKWH

1.5 — PcycTimer clock

pulse width

Both edge specification t

TCKWL

2.5 —

Oscillation settling time t

ROSC

3 — s 23.49

SCI Asynchronization t

SCYC

4 — Pcyc

*

23.50Input clock

cycle

Clock synchronization 6 — 23.51

Input clock rise time t

SCKR

— 1.5 23.50

Input clock fall time t

SCKF

— 1.5

Input clock pulse width t

SCKW

0.4 0.6 tscyc

Transmission data delay time t

TXD

— 100 ns 23.51

Receive data setup time (clock

synchronization)

t

RXS

100 —

Receive data hold time (clock

synchronization)

t

RXH

100 —

RTS delay time t

RTSD

— 100

CTS setup time (clock synchronization) t

CTSS

100 —

CTS hold time (clock synchronization) t

CTSH

100 —

Port Output data delay time t

PORTD

— 17 ns 23.52

Input data setup time t

PORTS1

15 —

Input data hold time t

PORTH1

8 —

Input data setup time t

PORTS2

tcyc +

15

—

Input data hold time t

PORTH2

8 —

Input data setup time t

PORTS3

3 × tcyc

+ 15

—

Input data hold time t

PORTH3

8 —

DMAC DREQ setup time t

DRQS

6 — ns 23.53

DREQ hold time t

DREQH

4 —

DRAK delay time t

DRAKD

— 10 23.54

Note: * Pcyc is the P clock cycle.