Rev. 5.00, 09/03, page 320 of 760

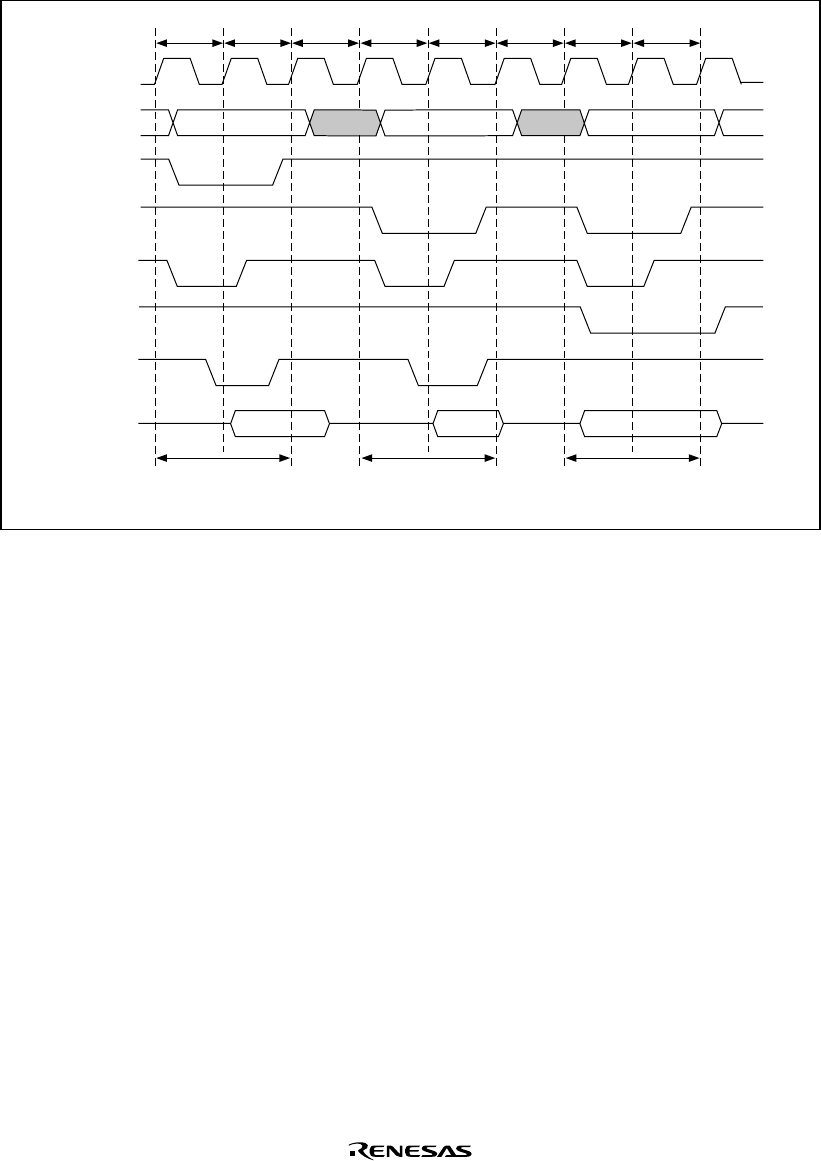

T

1

CKIO

CSm

CSn

A

25 to A0

BS

RD/WR

RD

D31 to D0

T

2

Twait T

1

T

2

Twait T

1

T

2

Area m read

Area m inter-access wait specification Area n inter-access wait specification

Area n space read Area n space write

Figure 10.40 Waits between Access Cycles

10.3.8 Bus Arbitration

When a bus release request (BREQ) is asserted from an external device, buses are released after

the bus cycle being executed is completed and a bus grant signal (BACK) is output. The bus is not

released during burst transfers for cache fills or write-back, or TAS instruction execution between

the read cycle and write cycle. Bus arbitration is not executed in multiple bus cycles that are

generated when the data bus width is shorter than the access size; i.e. in the bus cycles when

longword access is executed for the 8-bit memory. At the negation of BREQ, BACK is negated

and bus use is restarted. See Appendix A.1, Pin States, for the pin states when the bus is released.

The SH7709S sometimes needs to retrieve a bus it has released. For example, when memory

generates a refresh request or an interrupt request internally, the SH7709S must perform the

appropriate processing. The SH7709S has a bus request signal (IRQOUT) for this purpose. When

it must retrieve the bus, it asserts the IRQOUT signal. Devices asserting an external bus release

request receive the assertion of the IRQOUT signal and negate the BREQ signal to release the bus.

The SH7709S retrieves the bus and carries out the processing.