Rev. 5.00, 09/03, page 468 of 760

In transmitting serial data, the SCI operates as follows:

1. The SCI monitors the TDRE bit in SCSSR. When TDRE is cleared to 0 the SCI recognizes

that the transmit data register (SCTDR) contains new data, and transfers this data from SCTDR

into the transmit shift register (SCTSR).

2. After loading the data from SCTDR into SCTSR, the SCI sets the TDRE bit to 1 and starts

transmitting. If the transmit-data-empty interrupt enable bit (TIE) in SCSCR is set to 1, the SCI

requests a transmit-data-empty interrupt (TXI) at this time. Serial transmit data is transmitted

in the following order from the TxD pin:

a. Start bit: One 0-bit is output.

b. Transmit data: Seven or eight bits are output, LSB first.

c. Multiprocessor bit: One multiprocessor bit (MPBT value) is output.

d. Stop bit: One or two 1-bits (stop bits) are output.

e. Marking: Output of 1-bits continues until the start bit of the next transmit data.

3. The SCI checks the TDRE bit when it outputs the stop bit. If TDRE is 0, the SCI transfers data

from SCTDR into SCTSR, outputs the stop bit, then begins serial transmission of the next

frame. If TDRE is 1, the SCI sets the TEND bit in SCSSR to 1, outputs the stop bit, then

continues output of 1 bits in the mark state. If the transmit-end interrupt enable bit (TEIE) in

SCSCR is set to 1, a transmit-end interrupt (TEI) is requested at this time.

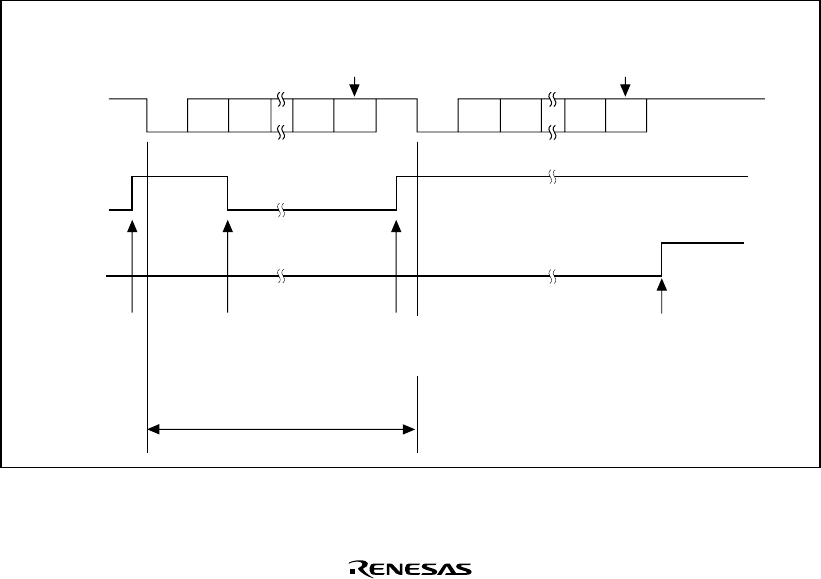

Figure 14.14 shows SCI transmission with a multiprocessor format.

TDRE

TEND

TXI interrupt

request

generated

TEI interrupt

request

generated

Writes data to TDR

with the TXI interrupt

processing routine

and clears TDRE

bit to 0

1 frame

01

1 1

0/1 0 1

Multi-

processor

bit

Serial

data

Start

bit

Data

Stop

bit

Start

bit

Data

Stop

bit

Idle (mark

)

state

D

0

D

1

D

7

D

0

D

1

D

7

0/1

Multi-

processor

bit

TXI interrupt

request

generated

Figure 14.14 Example of SCI Multiprocessor Transmit Operation

(8-Bit Data with Multiprocessor Bit and One Stop Bit)