Rev. 5.00, 09/03, page 162 of 760

7.2.9 Break Control Register (BRCR)

BRCR sets the following conditions:

1. Channels A and B are used in two independent channels condition or under the sequential

condition.

2. A break is set before or after instruction execution.

3. A break is set by the number of execution times.

4. Determine whether to include data bus on channel B in comparison conditions.

5. Enable PC trace.

6. Enable the ASID check.

The break control register (BRCR) is a 32-bit read/write register that has break conditions match

flags and bits for setting a variety of break conditions. A power-on reset initializes BRCR to

H'00000000.

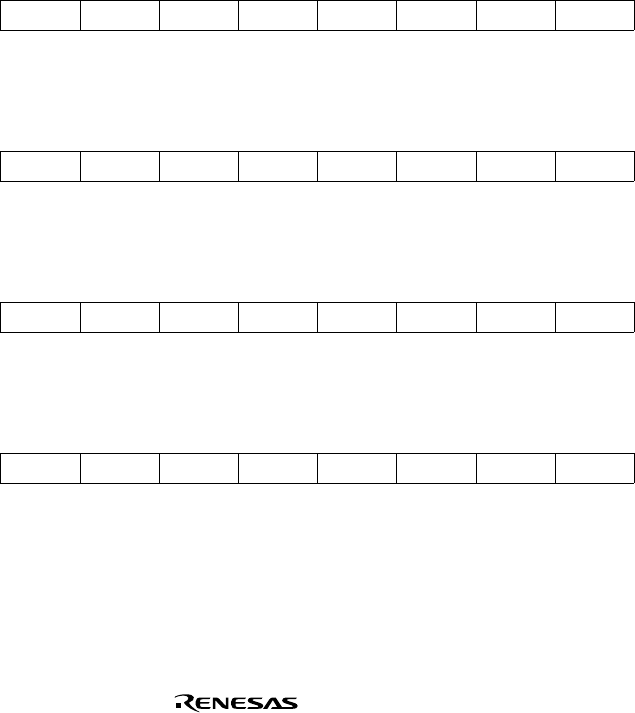

Bit: 31 30 29 28 27 26 25 24

————————

Initial value:00000000

R/W:RRRRRRRR

Bit: 23 22 21 20 19 18 17 16

——BASMABASMB————

Initial value:00000000

R/W:RRR/WR/WRRRR

Bit: 15 14 13 12 11 10 9 8

SCMFCA SCMFCB SCMFDA SCMFDB PCTE PCBA — —

Initial value:00000000

R/W: R/W R/W R/W R/W R/W R/W R R

Bit:76543210

DBEB PCBB — — SEQ — — ETBE

Initial value:00000000

R/W: R/W R/W R R R/W R R R/W

Bits 31 to 22—Reserved: These bits are always read as 0. The write value should always be 0.