Rev. 5.00, 09/03, page 496 of 760

15.3.3 Data Format

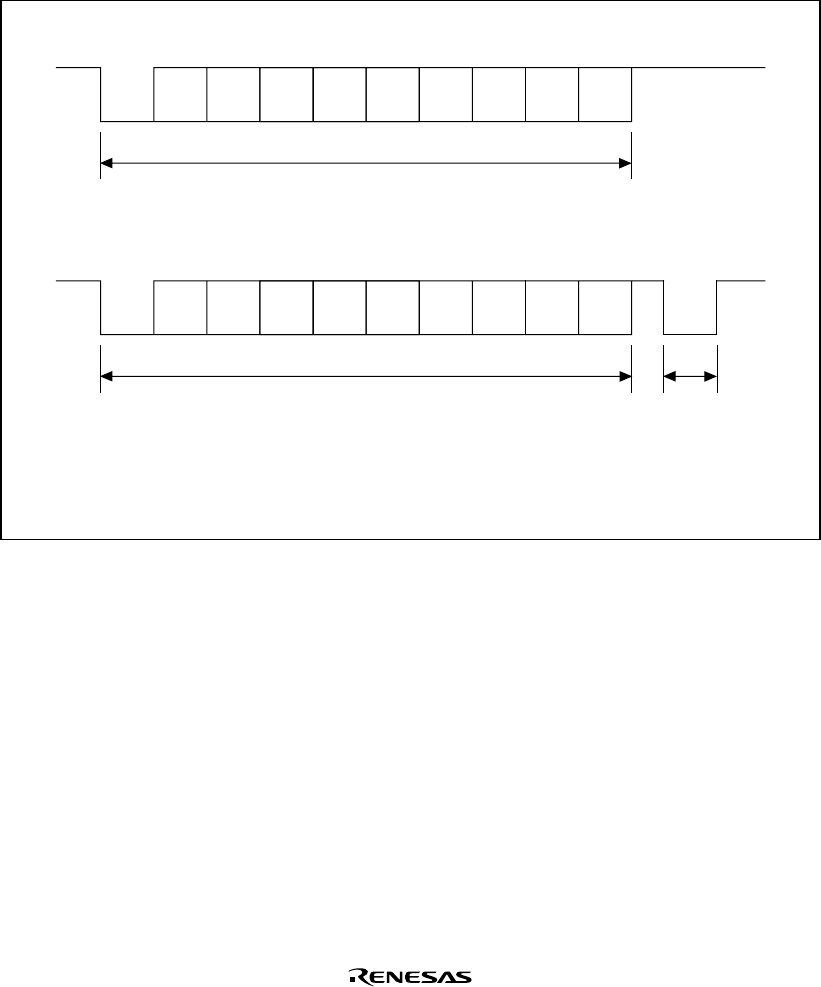

Figure 15.3 shows the data format for the smart card interface. In this mode, parity is checked

every frame while receiving and error signals sent to the transmitting side whenever an error is

detected so that data can be re-transmitted. During transmission, error signals are sampled and data

re-transmitted whenever an error signal is detected.

Ds D0 D1 D2 D3 D4 D5 D6 D7

Dp

With no parity error

Transmitting station output

Ds D0 D1 D2 D3 D4 D5 D6 D7

Dp DE

With parity error

Transmitting station output

Receiving

station output

Ds:

D0−D7:

Dp:

DE:

Start bit

Data bits

Parity bit

Error signal

Figure 15.3 Data Format for Smart Card Interface

The operating sequence is:

1. The data line is high-impedance when not in use and is fixed high with a pull-up register.

2. The transmitting side starts one frame of data transmission. The data frame starts with a start

bit (Ds, low level). The start bit is followed by eight data bits (D0–D7) and a parity bit (Dp).

3. On the smart card interface, the data line returns to high-impedance after this. The data line is

pulled high with a pull-up register.

4. The receiving side checks parity. When the data is received normally with no parity errors, the

receiving side then waits to receive the next data. When a parity error occurs, the receiving

side outputs an error signal (DE, low level) and requests re-transfer of data. The receiving

station returns the signal line to high-impedance after outputting the error signal for a specified

period. The signal line is pulled high with a pull-up register.