Rev. 5.00, 09/03, page 486 of 760

TEND Flag and TE Bit Processing: The TEND flag is set to 1 during transmission of the stop bit

of the last data. Consequently, if the TE bit is cleared to 0 immediately after setting of the TEND

flag has been confirmed, the stop bit will be in the process of transmission and will not be

transmitted normally. Therefore, the TE bit should not be cleared to 0 for at least 0.5 serial clock

cycles (or 1.5 cycles if two stop bits are used) after setting of the TEND flag is confirmed.

Receive Error Flags and Transmitter Operation (Synchronous Mode Only): When a receive

error flag (ORER, PER, or FER) is set to 1, the SCI will not start transmitting even if TDRE is set

to 1. Be sure to clear the receive error flags to 0 before starting to transmit. Note that clearing RE

to 0 does not clear the receive error flags.

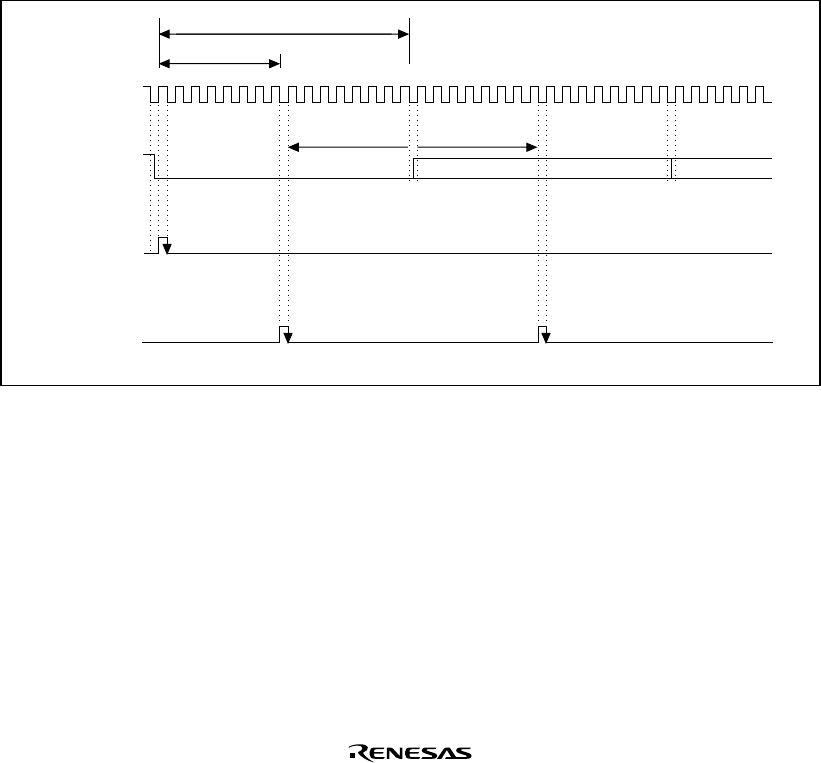

Receive Data Sampling Timing and Receive Margin in Asynchronous Mode: In asynchronous

mode, the SCI operates on a base clock of 16 times the transfer rate frequency. In receiving, the

SCI synchronizes internally with the falling edge of the start bit, which it samples on the base

clock. Receive data is latched at the rising edge of the eighth base clock pulse (figure 14.24).

0 1 2 3 4 5 6 7 8 9 101112131415 0 1 2 3 4 5 6 7 8 9 101112131415 0 1 2 3 4 5

Base clock

Receive

data (RxD)

Synchro-

nization

sampling

timing

Data

sampling

timing

8 clocks

16 clocks

Start bit

−7.5 clocks

+7.5 clocks

D0 D1

Figure 14.24 Receive Data Sampling Timing in Asynchronous Mode