Rev. 5.00, 09/03, page 301 of 760

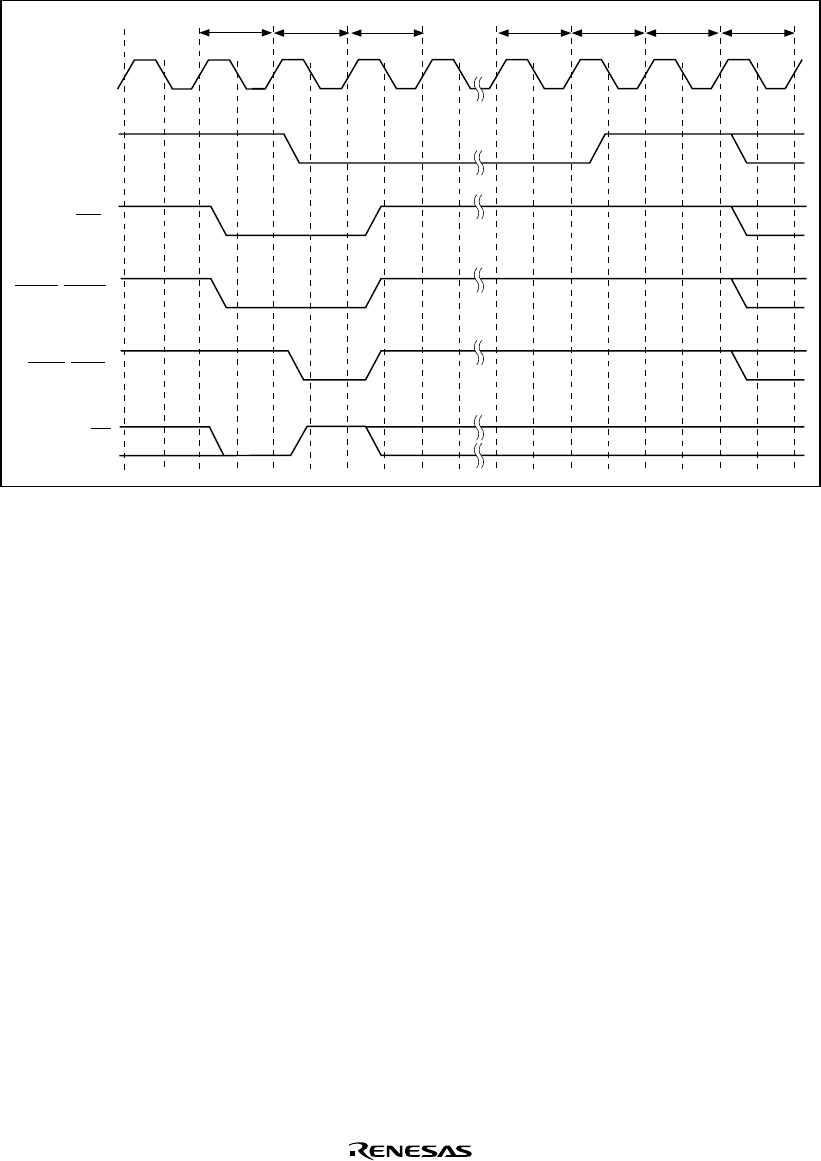

TRs1

CKIO

RD/WR

CSn

RAS3U, RAS3L

CASU, CASL

CKE

(TRs2) (TRs2) TRs3 (Tpc) (Tpc)

Tp

Figure 10.27 Synchronous DRAM Self-Refresh Timing

• Relationship between Refresh Requests and Bus Cycle Requests

If a refresh request is generated during execution of a bus cycle, execution of the refresh is

deferred until the bus cycle is completed. If a refresh request occurs when the bus has been

released by the bus arbiter, refresh execution is deferred until the bus is acquired. If a match

between RTCNT and RTCOR occurs while a refresh is waiting to be executed, so that a new

refresh request is generated, the previous refresh request is eliminated. In order for refreshing

to be performed normally, care must be taken to ensure that no bus cycle or bus right occurs

that is longer than the refresh interval. When a refresh request is generated, the IRQOUT pin is

asserted (driven low). Therefore, normal refreshing can be performed by having the IRQOUT

pin monitored by a bus master other than the SH7709S requesting the bus, or the bus arbiter,

and returning the bus to the SH7709S. When refreshing is started, and if no other interrupt

request has been generated, the IRQOUT pin is negated (driven high).