Rev. 5.00, 09/03, page 385 of 760

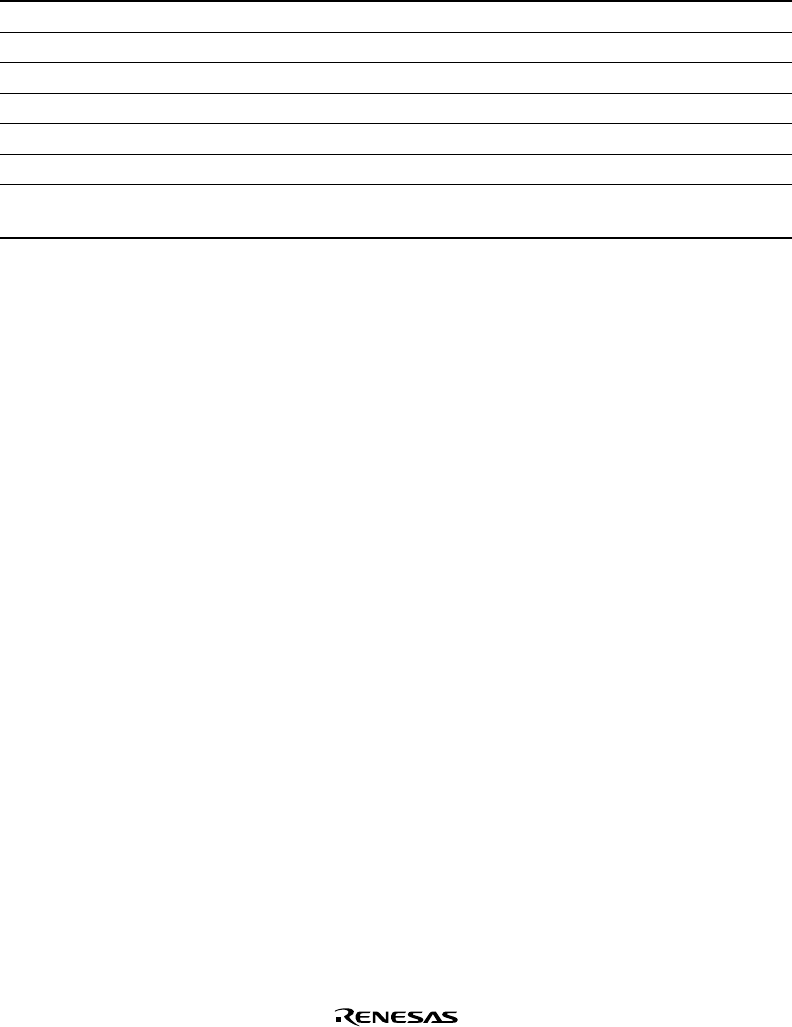

As a result, the values in the DMAC are as shown in table 11.10 when the fourth transfer ends,

depending on whether the address reload function is on or off.

Table 11.10 Values in DMAC after End of Fourth Transfer

Items Address reload on Address reload off

SAR H'04000080 H'04000090

DAR H'003FFFFC H'003FFFFC

DMATCR H'0000007C H'0000007C

Bus right Released Held

DMAC operation Stops Keeps operating

Interrupt Not generated Not generated

Transfer request source flag

clearing

Executed Not executed

Notes: 1. An interrupt is generated regardless of whether the address reload function is on or off,

if transfers are executed until the value in DMATCR reaches 0 and the IE bit in CHCR

has been set to 1.

2. The transfer request source flag is cleared regardless of whether the address reload

function is on or off, if transfers are executed until the value in DMATCR reaches 0.

3. Specify burst mode when using the address reload function. This function may not be

correctly executed in cycle-steal mode.

4. Set a multiple of four in DMATCR when using the address reload function. This function

may not be correctly executed if other values are specified.

11.5.3 Example of DMA Transfer between External Memory and SCIF Transmitter

(Indirect Address On)

In this example, DMA transfer is performed between the external memory specified by indirect

address (transfer source) and the SCIF transmitter (transfer destination) using DMAC channel 3.

Table 11.11 shows the transfer conditions and register settings. In addition, the trigger for the

number of transmit FIFO data bytes is set to 1 (TTRG1 = TTRG0 = 1 in SCFCR).