Rev. 5.00, 09/03, page 386 of 760

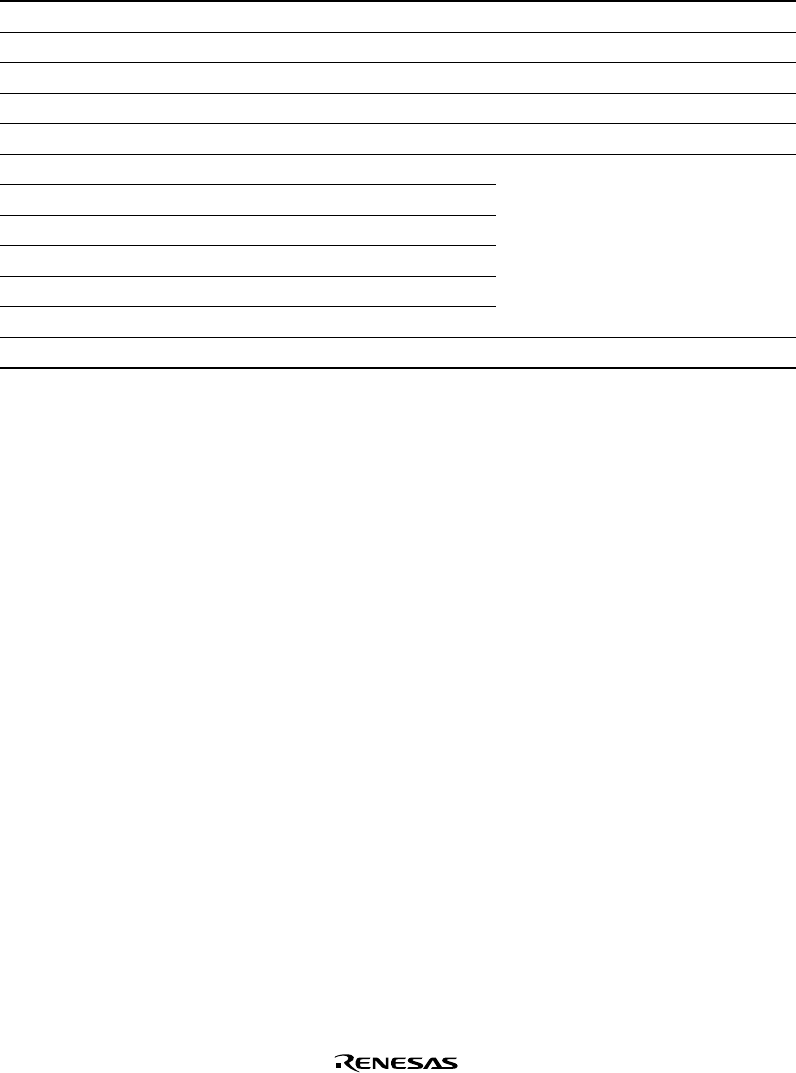

Table 11.11 Transfer Conditions and Register Settings for Transfer between External

Memory and SCIF Transmitter

Transfer Conditions Register Setting

Transfer source: External memory SAR3 H'00400000

Value stored in address H'00400000 — H'00450000

Value stored in address H'04500000 — H'55

Transfer destination: On-chip SCIF TDR2 DAR3 H'04000156

Number of transfers: 10 DMATCR3 H'0000000A

Transfer source address: Incremented CHCR3 H'00011C01

Transfer destination address: Fixed

Transfer request source: SCIF (TXI2)

Bus mode: Cycle-steal

Transfer unit: Byte

No interrupt request generated at end of transfer

Channel priority order: 0 > 1 > 2 > 3 DMAOR H'0001

If the indirect address is on, data stored in the address set in SAR is not used as transfer source

data. In the indirect address, after the value stored in the address set in SAR is read, that read value

is used as an address again, and the value stored in that address is read and stored in the address

set in DAR.

In the example shown in table 11.11, when an SCIF transfer request is generated, the DMAC reads

the value in address H'00400000 set in SAR3. Since the value H'00450000 is stored in that

address, the DMAC reads the value H'00450000. Next, the DMAC uses that read value as an

address again, and reads the value H'55 stored in that address. Then, the DMAC writes the value

H'55 to address H'04000156 set in DAR3; this completes one indirect address transfer.

In the indirect address, when data is read first from the address set in SAR3, the data transfer size

is always longword regardless of the settings of the TS0 and TS1 bits that specify the transfer data

size. However, whether the transfer source address is fixed, incremented, or decremented is

specified by the SM0 and SM1 bits. Therefore, in this example, though the transfer data size is

specified as byte, the value in SAR3 is H'00400004 when one transfer ends. Write operations are

the same as in normal dual address transfer.