Rev. 5.00, 09/03, page 720 of 760

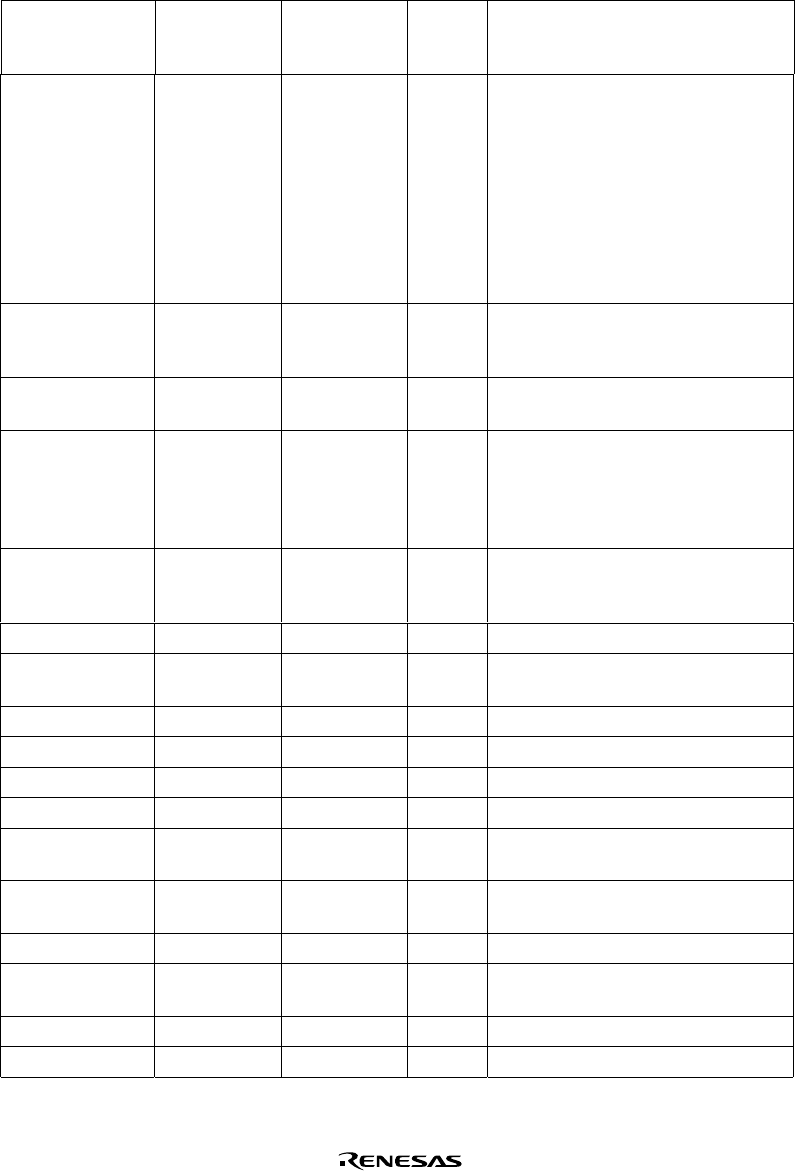

Pin

Pin No.

(FP-208C,

FP-208E)

Pin No.

(BP-240A)

I/O Function

A25 to A0 86, 84, 82, 80,

78 to 72, 70,

68 to 60, 58,

56 to 53

V12, T12,

V11, W10,

V10, U9, T9,

V9, W9, T8,

U8, W8, U7,

V7, W7, T6,

U6, V6, W6,

T5, U5, W5,

W4, V5, V3,

V4

O Address bus

D31 to D24/

PTB[7] to PTB[0]

13 to 18, 20,

22

F4, G1, G2,

G3, G4, H1,

H3, J1

I/O Data bus / I/O port

D23 to D16/

PTA[7] to PTA[0]

23 to 26, 28,

30 to 32

J2, J4, J3, K2,

K1, L2, L1, M4

I/O Data bus / I/O port

D15 to D0 34, 36 to 44,

46, 48 to 52

M2, N4, N3,

N2, N1, P4,

P3, P2, P1,

R4, T4, T3,

T1, R2, U2,T2

I/O Data bus

MCS[7:0]/

PTC[7:0]/

PINT[7:0]

177 to

180,185 to

188

B11, D11,

C11, B10, D9,

B9, A9, D8

I/O Mask ROM chip select / I/O port /

port interrupt request

WAKEUP/PTD[3] 182 D10 I/O Wakeup / I/O port

RESETOUT/

PTD[2]

184 C9 I/O Reset output / I/O port

DRAK0/PTD[1] 189 C8 I/O DMA control pin / I/O port

DRAK1/PTD[0] 190 B8 I/O DMA control pin / I/O port

DREQ0/PTD[4] 191 A8 I DMA transfer request 0 / input port

DREQ1/PTD[6] 192 D7 I DMA transfer request 1 / input port

AN[5:0]/PTL[5:0] 204 to 199 C4, A5, D4,

C5, D5, A6

I Analog input pin / input port

AN[7:6]/DA[1:0]/

PTL[7:6]

207, 206 B3, B5 I/O Analog I/O pin / input port

CS6/CE1B 102 V15 O Chip select 6 / PCMCIA CE1B

CS5/CE1A/

PTK[3]

101 W16 I/O Chip select 5 / PCMCIA CE2B / I/O

port

CS4/PTK[2] 100 U16 I/O Chip select 4 / I/O port

CS3/PTK[1] 99 W15 I/O Chip select 3 / I/O port