Rev. 5.00, 09/03, page 482 of 760

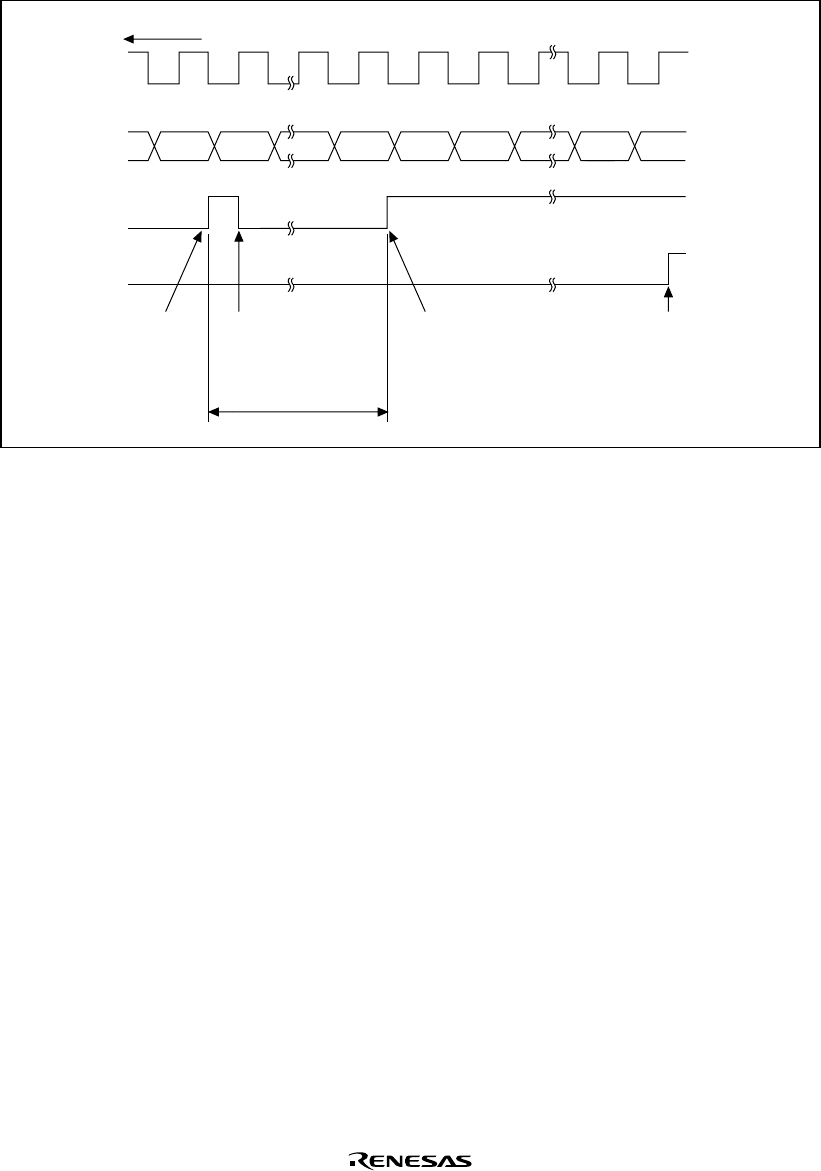

Bit 7 Bit 0 Bit 7 Bit 0 Bit 1 Bit 6

Serial

clock

Serial

data

Transfer direction

Bit 7

RXI interrupt

handler reads data

and clears RDRF

bit to 0

1 frame

RXI interrupt

request

generated

RXI interrupt

request

generated

ERI interrupt

request generated

by overrun error

RDRF

ORER

Figure 14.22 Example of SCI Receive Operation

Transmitting and Receiving Serial Data Simultaneously (Synchronous Mode): Figure 14.23

shows a sample flowchart for transmitting and receiving serial data simultaneously. The procedure

for setting the SCI to transmit and receive serial data simultaneously is:

1. SCI status check and transmit data write: Read the serial status register (SCSSR), check that

the TDRE bit is 1, then write transmit data in the transmit data register (SCTDR) and clear

TDRE to 0. The TXI interrupt can also be used to determine if the TDRE bit has changed from

0 to 1.

2. Receive error handling: If a receive error occurs, read the ORER bit in SCSSR to identify the

error. After executing the necessary error handling, clear ORER to 0. Transmitting/receiving

cannot resume if ORER remains set to 1.

3. SCI status check and receive data read: Read the serial status register (SCSSR), check that

RDRF is set to 1, then read receive data from the receive data register (SCRDR) and clear

RDRF to 0. The RXI interrupt can also be used to determine if the RDRF bit has changed from

0 to 1.

4. To continue transmitting and receiving serial data: Read the RDRF bit and SCRDR, and clear

RDRF to 0 before the MSB (bit 7) of the current frame is received. Also read the TDRE bit to

check whether it is safe to write (if it reads 1); if so, write data in SCTDR, then clear TDRE to

0 before the MSB (bit 7) of the current frame is transmitted.