Rev. 5.00, 09/03, page 699 of 760

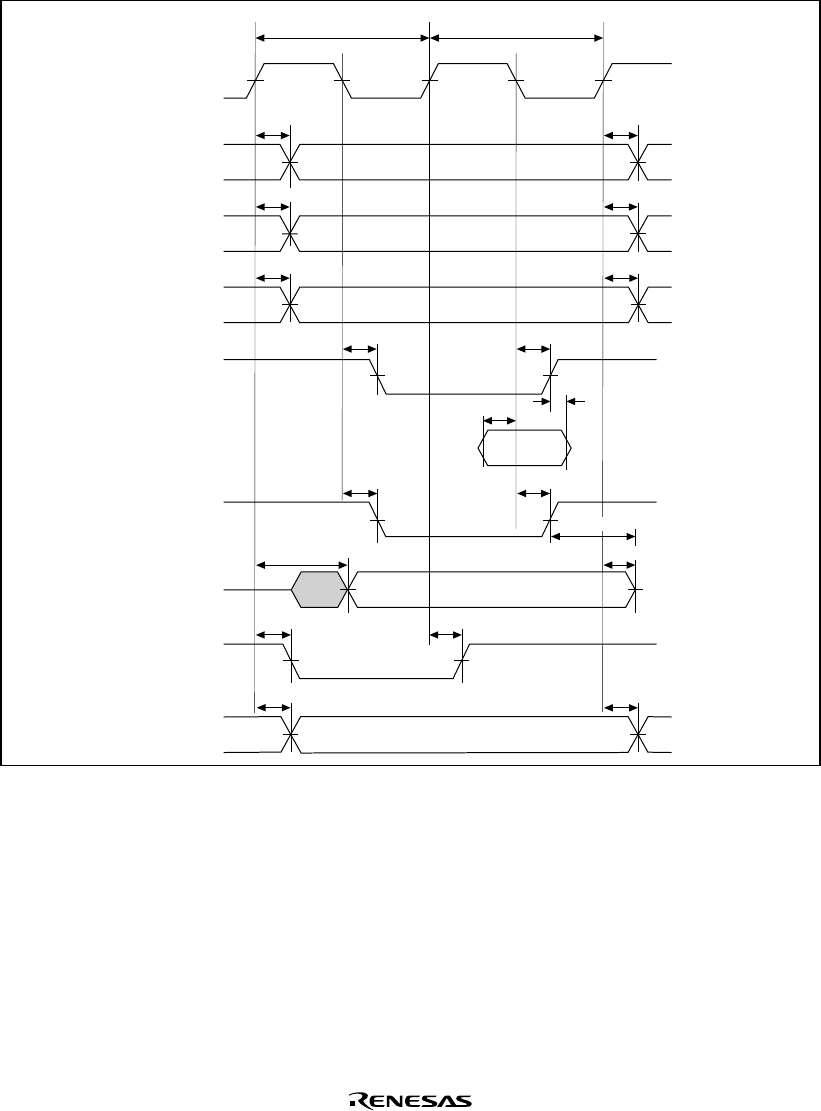

23.3.7 PCMCIA Timing

T

pcm1

T

pcm2

CKIO

A25 to A0

CExx

RD/WR

RD

D15 to D0

WE1

D15 to D0

BS

DACKn

t

AD

t

AD

t

CSD1

t

CSD1

t

RWD

t

RSD

t

RSD

t

RWD

t

DAKD1

t

DAKD1

t

WED

t

WDD1

t

WED

t

RDS1

t

RDH1

t

BSD

t

BSD

t

WDH4

t

WDH1

(read)

(read)

(write)

(write)

Figure 23.40 PCMCIA Memory Bus Cycle (TED = 0, TEH = 0, No Wait)