G2

G2

G2

G2

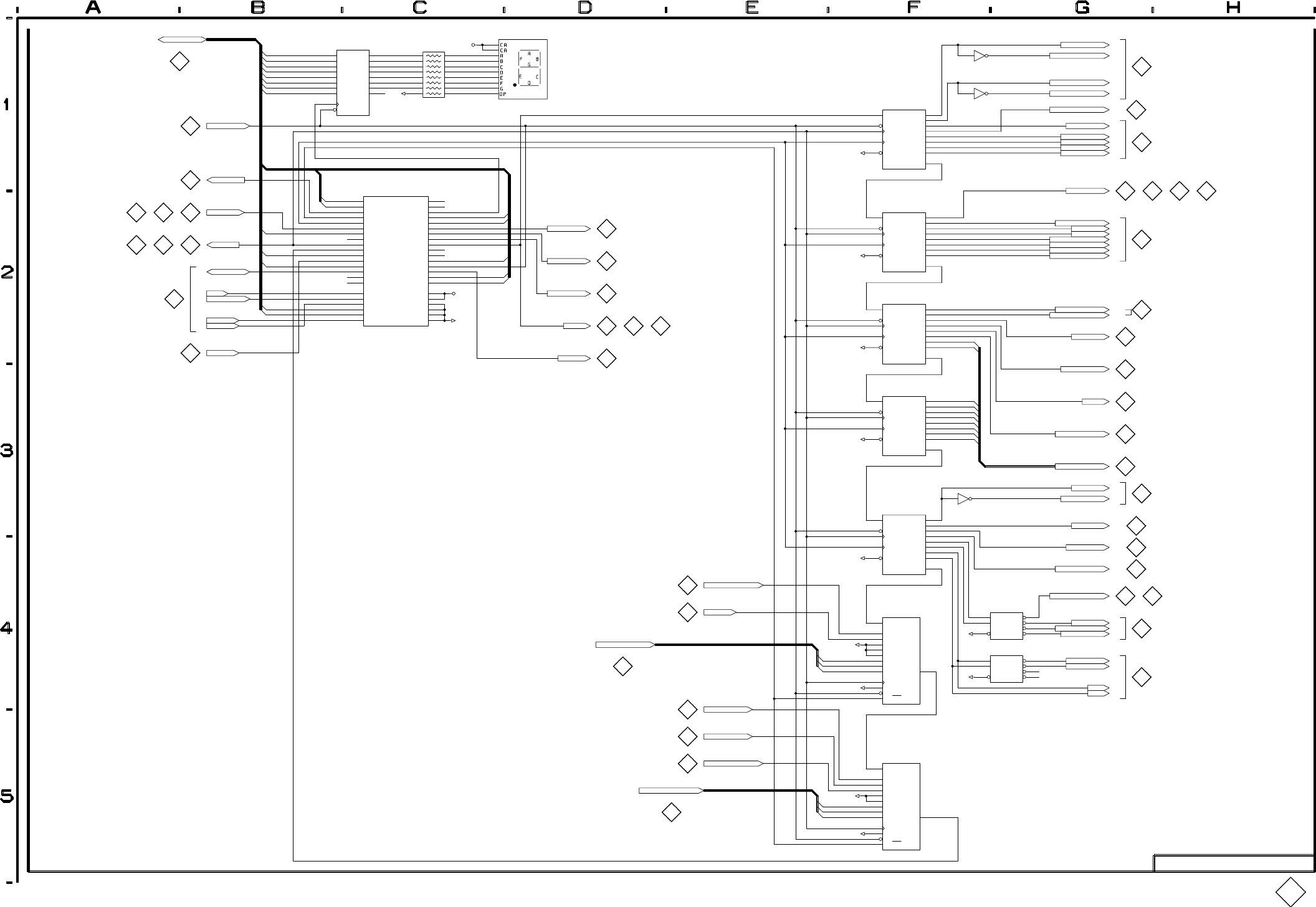

11

EQ_BYPASS

(EQ_BYPASS)

EYE/(JITTER)

SERIAL CONTROL

1 2

U144A

74F04

3

14

1

13

10

8

7

2

11

6

DS2

+5V

1 16

2 15

3 14

4 13

5 12

6 11

7 10

8 9

R299

330

D1

3

Q1

2

D2

4

Q2

5

D3

7

Q3

6

D4

8

Q4

9

D5

13

Q5

12

D6

14

Q6

15

D7

17

Q7

16

D8

18

Q8

19

CLK

11

CLR

1

U116

74ALS273

H3

1

D[0..23]

D8

D9

D10

D11

D12

D13

D[0..23]

D2

8

A2

3

B2

7

G2

8

A1

11

(TRIG)

(DSPRST)

D14

D15

IO0

2

IO1

3

IO2

4

IO3

5

IO4

6

IO5

7

IO6

8

IO7

9

IO8

14

IO9

15

IO10

16

IO11

17

IO12

18

IO13

19

IO14

20

IO15

21

IO16

24

IO17

25

IO18

26

IO19

27

IO20

28

IO21

29

IO22

30

IO23

31

IO24

36

IO25

37

IO26

38

IO27

39

IO29

41

IO30

42

IO31

43

CLK0/I2

13

CLK1/I5

35

VCC

44

GND

12

GND

23

GND

34

GND

1

VCC

22

IO28

40

I0

10

I1

11

I3

32

I4

33

U117

MACH110PLCC

D2

LED_STROBE

D8

D

SCTD

(DSPRST)

SCCLK

SCLO

SER

14

QA

15

QB

1

SRCLK

11

QC

2

SRCLR

10

QD

3

QE

4

RCLK

12

QF

5

G

13

QG

6

QH

7

QH

9

U95

74HC595

3

4

U144B

74F04

D

WIRE

D4

D4

D4

D4

D4

2

C2

3

A2

4

B1

9

A1 9

SSI_DIR_0

SSI_DIR_1

SSI_DIR_2

SSI_DIR_3

SSI_MODE

ER_CLEAR

JITTER/(EYE)

MAIN_RELOCK

F4

11

D5

D2

D2

D2

D2

D2

D2

9

E4

A2

3

F5

11

REFOUT_SEL0

REFOUT_SEL1

OFFSET_SEL0

OFFSET_SEL1

PH_SEL0

PH_SEL1

INTMCK_SEL

(STX_VERS)

STX_FREERUN

SM_TEST

SER

14

QA

15

QB

1

SRCLK

11

QC

2

SRCLR

10

QD

3

QE

4

RCLK

12

QF

5

G

13

QG

6

QH

7

QH

9

U96

74HC595

SER

14

QA

15

QB

1

SRCLK

11

QC

2

SRCLR

10

QD

3

QE

4

RCLK

12

QF

5

G

13

QG

6

QH

7

QH

9

U97

74HC595

D

A1

11

(DSPRST)

(DSPRST)

SCCLK

SCCLK

SCLO

SCLO

B4

7

A1

11

B2

7

B2

7

G1

8

(SYNTH1)

(SYNTH3)

(SYNTH2)

SCTD

D0

D5

D11

D10

D9

SRD

SCLO

SCLI

(GTRIG)

(RD)

(CEP0)

CKOUT

(TRIG)

SCCLK

TRI_SRD

LED_STROBE

SCTD

(ADC)

(DSPRST)

(SYNTH3)

(SYNTH1)

(SYNTH2)

(WR)

CSBLK

+5V

D

B2

7

A1

11

G1

8

A2

E5

F5

E5

E5

1

(PWR)

CKOUT

SCCLK

(GTRIG)

(SID_CE)

TRI_SRD

PRD

D3

D1

D4

D6

D7

C2

4

CSBLK

G1

8

(ADC)

(DSPRST)

SCCLK

SCLO

SER

14

QA

15

QB

1

SRCLK

11

QC

2

SRCLR

10

QD

3

QE

4

RCLK

12

QF

5

G

13

QG

6

QH

7

QH

9

U142

74HC595

AMPL0

AMPL1

AMPL2

AMPL3

AMPL4

AMPL5

AMPL6

AMPL7

AMPL8

AMPL9

D

D

WIRE

F3

9

A2

4

B5

5

A3

9

REFOUT_ON

SLOW

REF_RELOCK

D2

D2

11

D5 9

E4 3

F2 5

C1

6

A3

9

RED_BW_SEL

(STXDSP)

AMPL[0..9]

EJ_GAIN

STX_RST

(EJ_GAIN)

SER

14 15

QB

1

SRCLK

11

QC

2

SRCLR

10

QD

3

QE

4

RCLK

12

QF

5

G

13

QG

6

QH

7

QH

9

U141

74HC595

9

8

U144D

74F04

SCDATA

AMPL[0..9]

D

F3

2

(REAR_PANEL)

(DSPRST)

SCCLK

SCLO

E1

9

INSTAT[0..3]

H3

5

H5

11

(XLR)

EJ_UNLOCK

INSTAT[0..3]

SCCLK

(DSPRST)

SCLI

SER IN

1

A

2

B

3

C

4

D

5

E

10

F

11

G

12

H

14

QH

13

CLK

7

CK INH

6

SH/LD

15

CLR

9

U93

74HC166

A

14

Y0

12

B

13

Y1

11

Y2

10

G

15

Y3

9

U118B

74HC139

A

2

Y0

4

B

3

Y1

5

Y2

6

G

1

Y3

7

U118A

74HC139

INSTAT0

INSTAT1

INSTAT2

D

D

D

D

C1

C1

C1

6

D2

D2

G4

G4

11

(LOOPBK_EN)

(FP_EN)

(UNBAL_EN)

(OPTO_EN)

(EJ_BW0)

(EJ_BW1)

BW0

BW1

SERIAL STATUS

SER IN

1

A

2

B

3

C

4

D

5

E

10

F

11

G

12

H

14

QH

13

CLK

7

CK INH

6

SH/LD

15

CLR

9

U94

74HC166

SRDREFSTAT0

REFSTAT1

REFSTAT2

D

D

C2

4

C2

3

E2

9

REFSTAT[0..3]

PH_UNLOCK

SYNTH_UNLOCK

REFSTAT[0..3]

SCCLK

(DSPRST)

SCLI

AM 700

SERIAL CONTROL

PART OF A3 DIGITAL AUDIO BOARD

10

QA

SERIAL CONTROL PAL

REGISTER