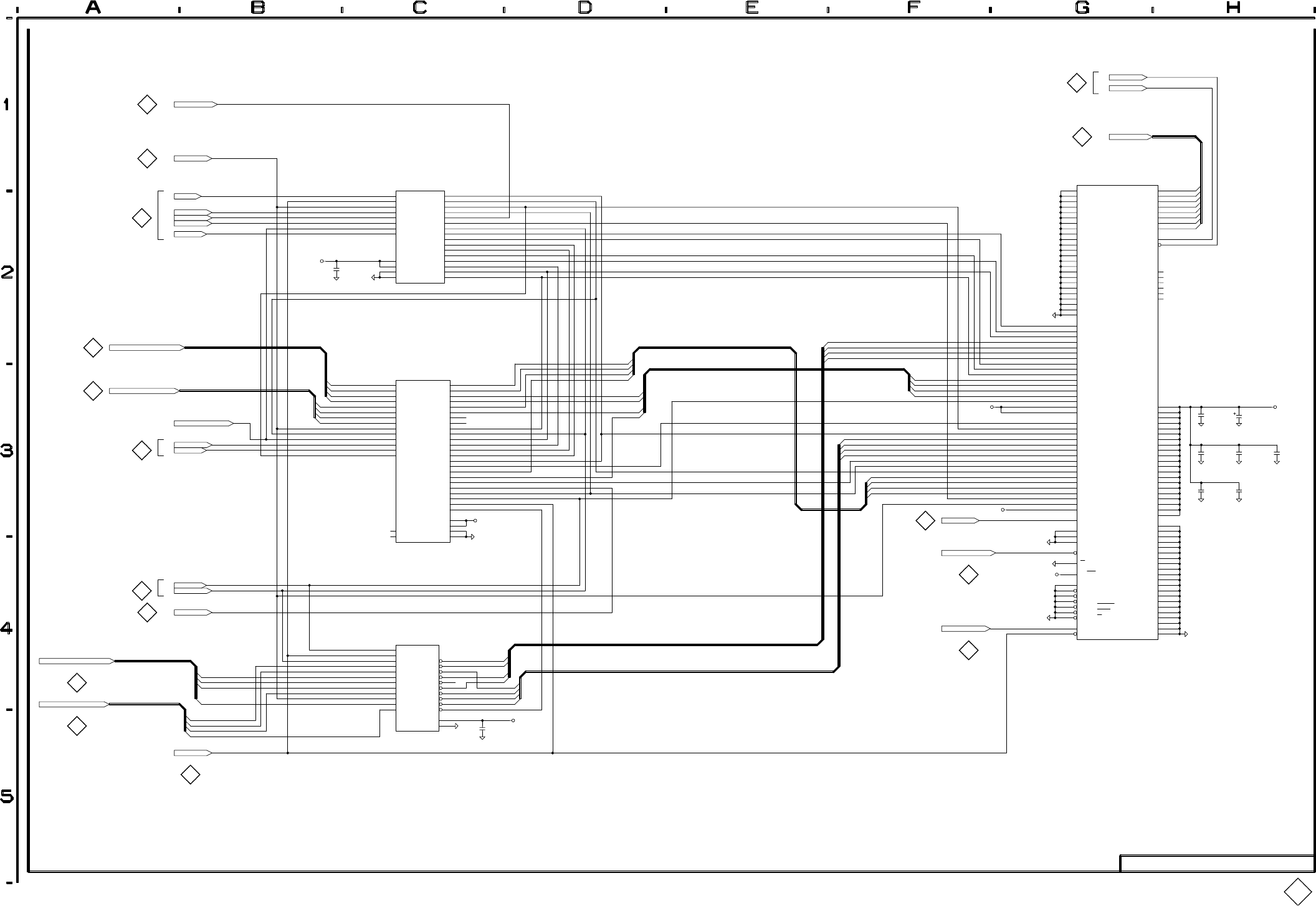

XFERCLK

TCLK

G2

G3

6

3CLK

ADCSELA

ADC_SELECT_A

TEST_CLK

C36

E36

H4

H4

H4

H5

H1

4

ADC3_CLK

(RESET)

ADC_SELECT_A

I0

1

I1

2

I2

13

I3

14

I4

15

I5

16

I6

27

I7

28

IO0

3

VCC

7

GND

8

IO1

4

IO2

5

IO3

6

IO4

9

IO5

10

IO6

11

IO7

12

IO8

17

IO9

18

IO10

19

IO11

20

IO12

23

IO13

24

IO14

25

IO15

26

GND

21

VCC

22

U117

EPM5032-25

ADCSELA: 0 = HI-BW DECIMATED BY 4

1 = HI-BW

A2LDE

A2RDE

A2LDS

TD[0..7]

STFLAG

TIDENT

TD0

TD1

TD2

TD3

TD[0..7]

G36

D0

49

D1

50

D2

53

D3

55

D4

56

D5

58

D6

59

D7

61

D8

62

D9

64

D10

65

D11

67

D12

68

D13

70

D14

71

D15

73

D16

74

D17

76

D18

77

D19

79

D20

80

D21

82

D22

84

D23

85

TD0

104

TD1

106

TD2

107

TD3

109

TD4

110

TD5

112

TD6

113

TD7

115

A1LD

17

A1LDS

19

A1LDE

20

A1RD

22

A1RDS

23

A1RDE

25

A1BCLK

26

A1SENSE

28

A1LSH0

29

A1LSH1

31

A1LSH2

32

A1LSH3

34

A1RSH0

38

A1RSH1

40

A1RSH2

41

A1RSH3

44

A1LSB/MSB

46

A2LD

7

A2LDS

8

A2LDE

10

A2RD

11

A2RDE

14

A2LSH0

124

A2LSH1

125

A2LSH2

127

A2LSH3

128

A2RDS

13

A2RSH0

130

A2RSH1

131

A2RSH2

1

A2RSH3

2

A2LSB/MSB

122

TRIG

16

EYEIN

121

EYECLK

119

EYEDS

118

XMITVERS

97

A/D

47

MCLK

37

RST

98

A2BCLK

4

A2SENSE

5

TIDENT

116

TCLK

103

DSP_RD

94

DSP_CE

91

DSP_WR

95

DSP_DATA/CTL

89

DSP_LSW/MSB

88

DSP_L/R

86

GND

132

GND

126

GND

120

GND

105

GND

99

GND

93

GND

78

GND

72

GND

66

GND

60

GND

54

GND

48

GND

42

GND

36

GND

30

GND

24

GND

18

GND

12

GND

6

VDD

129

VDD

123

VDD

114

VDD

102

VDD

96

VDD

90

VDD

81

VDD

75

VDD

69

VDD

63

VDD

57

VDD

51

VDD

45

VDD

39

VDD

27

VDD

21

VDD

15

VDD

9

NC

35

NC

43

NC

52

NC

83

NC

92

NC

101

DSP

100

TX/RX

117

GND

111

VDD

33

VDD

3

GND

87

VDD

108

U120

ADG311 SAMPLE TRANSMITER

TD4

TD5

TD6

TD7

TIDENT

TCLK

A1LD

A1LDS

A1LDE

A2RDS

A2BCLK

A1LD

A1RD

TEST_CLK

A1RDS

A1LDS

ADC1.1.START

A1LDE

A1RDE

TEST_PATTERN1

TEST_PATTERN0

ADC1_L/(R)

ADC2_CC

ADC3_L/(R)

ADC2_CLK

TEST_ENABLE

ADC1_DATA

C3

0.1UF

+5VD

3LRCLK

1DATA

2IBCLK

2CONVC

F3

6

E3

6

3DATA

2LDATA

CHB_ATTEN[0..3]

CHB_GAIN[0..3]

TEST_ENABLE

CHB_GAIN[0..3]

CHB_ATTEN[0..3]

H4

H44

ADC_SELECT_A

CHB_ATTEN3

CHB_ATTEN2

CHB_ATTEN1

CHB_ATTEN0

CHB_GAIN3

CHB_GAIN2

CHB_GAIN1

CHB_GAIN0

A2RDE

TEST_ENABLE

ADC2_LDATA

ADC3_DATA

A2LDS

IN0

1

IN1

2

IN2

3

IN3

19

IN4

20

IN5

21

IN6

22

IN7

23

IN8

24

IN9

25

IN10

41

IN11

42

IN12

43

IN13

44

IO0

5

IO1

6

IO2

7

IO3

8

IO4

9

IO5

10

IO6

40

IO7

39

IO8

38

IO9

37

IO10

36

IO11

35

IO12

18

IO13

17

IO14

16

IO15

15

IO16

14

IO17

13

IO18

27

IO19

28

IO20

29

IO21

30

IO22

31

IO23

32

VCC

11

GND

33

VCC

12

GND

34

NC

4

NC

26

U118

ATV2500H-35

A2RS1

A2RS2

A1RS1

A1RS3

A2RS3

A1RS2

A2LDE

TEST_PATTERN1

TEST_PATTERN0

ADC1.1.START

A1LDE

A1RDE

ADC1_L/(R)

A1RS0

A2RS0

A2RS1

A2RS2

A2RS3

A1LS0

A1LS1

A1LS2

A1LS3

A1RS0

A1RS1

A1RS2

A1RS3

A2LS0

A2LS1

A2LS2

A2LS3

+5VD

A1RD

A1RDS

A1RDE

A1SENSE

A1MSB/(LSB)

A2LD

A2LDS

A2LDE

A2RD

ADC1_CLK

C4

0.1UF

C1

10UF

C5

0.1UF

C6

0.1UF

C7

0.1UF

+5VD

C8

0.1UF

C9

0.1UF

TRIGGER

(XMITVERS)

A2RDS

A2RDE

A2BCLK

A2MSB/(LSB)

ADC_SELECT_A

+5VD

+5VD

(XMITVERS)

TRIGOUT

A2RS0

A2RS1

A2RS2

A2RS3

B3

6

E3

6

A1RS0

A2RS0

A2RDS

A2LD

A2RD

ADC2_RDATA

ADC1_CLK

(RESET)

ADC1.1.LATCH_L_R

+5VD

1L/(R)

1SCLK

ADC1_L/(R)

ADC1_CLK

H2

H24

CHA_ATTEN[0..3]

CHA_GAIN[0..3]

E4

6

E4

6

CHA_ATTEN[0..3]

CHA_GAIN[0..3]

CHA_ATTEN0

CHA_ATTEN1

CHA_ATTEN2

CHA_ATTEN3

2RDATA

H44

ADC1_CLK

(RESET)

ADC_SELECT_A

ADC1_L/(R)

I1/CLK

1

I2

2

I3

3

I4

4

I5

5

I6

6

I7

7

I8

8

I9

9

I10

10

I11

11

I12

13

IO10

14

IO9

15

IO8

16

IO7

17

IO6

18

IO5

19

IO4

20

IO3

21

IO2

22

IO1

23

VCC

24

GND

12

U119

22V10

ADC1.1.LATCH_L_R

A2LS0

A2LS1

A1LS2

A2LS3

A1LS0

A1LS1

A2LS2

A1LS3

12.288MHz

H1

4

CLK

(RESET)

C2

0.1UF

+5VD

ARESET

CHA_GAIN3

CHA_GAIN1

CHA_GAIN2

CHA_GAIN0

G2

6

AM 700 SAMPLE TRANSMITTER

PART OF A1A1 ANALOG ACQUISITION BOARD

5